___ ____ ___ ____ _ ____ ____ ___

/ \ | \ / _]| \ | | / || \ / _]

| || o ) [_ | _ || | | o || _ | / [_

| O || _/ _]| | || |___ | || | || _]

| || | | [_ | | || || _ || | || [_

\___/ |__| |_____||__|__||_____||__|__||__|__||_____|

This documentation is also available at ReadTheDocs here.

- Overview

- Prerequisites

- Quick Start

- Updating OpenLANE

- Setting up OpenLANE

- OpenLANE Architecture

- Regression And Design Configurations Exploration

- Hardening Macros

- Chip Integration

- Commands and Configurations

- How To Contribute

- Authors

- Additional Material

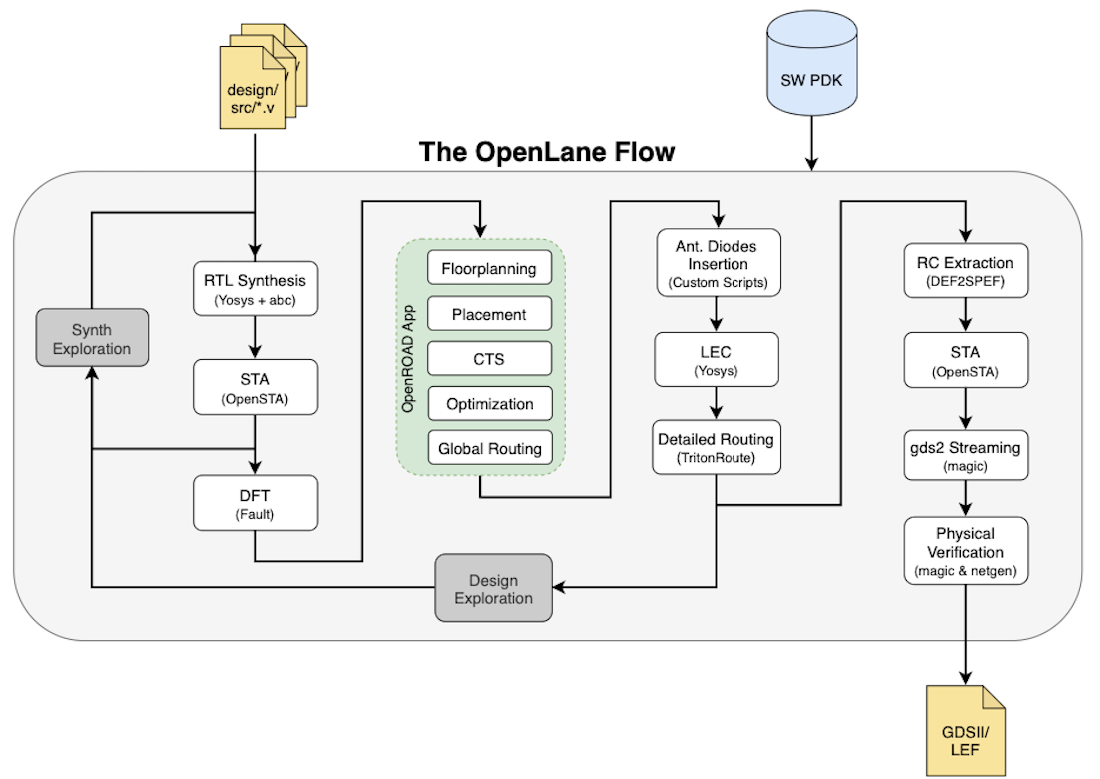

OpenLANE is an automated RTL to GDSII flow based on several components including OpenROAD, Yosys, Magic, Netgen, Fault, OpenPhySyn, CVC, SPEF-Extractor, CU-GR, Klayout and custom methodology scripts for design exploration and optimization. The flow performs full ASIC implementation steps from RTL all the way down to GDSII - this capability will be released in the coming weeks with completed SoC design examples that have been sent to SkyWater for fabrication.

Join the community on slack!

To use the latest stable release of OpenLane, please go here.

- Docker (ensure docker daemon is running) -- tested with version 19.03.12, but any recent version should suffice

To use the latest stable release of OpenLane, please go here.

You can start setting up the skywater-pdk and openlane by running:

git clone https://github.com/efabless/openlane.git

cd openlane/

make openlane

# Default PDK_ROOT is $(pwd)/pdks. If you want to install the PDK at a differnt location, uncomment the next line.

#export PDK_ROOT=<absolute path to where skywater-pdk and open_pdks will reside>

make pdk

make test # This is to test that the flow and the pdk were properly installedThis should produce a clean run for the spm. The final layout will be generated here: ./designs/spm/runs/openlane_test/results/magic/spm.gds.

To run the regression test, which tests the flow against all available designs under ./designs/ vs the the benchmark results, run the following command:

make regression_testYour results will be compared with: sky130_fd_sc_hd.

After running you'll find a directory added under ./regression_results/ it will contain all the reports needed for you to know whether you've been successful or not. Check this for more details.

Note: if flow_status is flow_failed, that means the design failed. Any reported statistics from any run after the failure of the design is reported as -1 as well.

Now you can skip forward to running openlane.

-

The Makefile should do the following when you run the above command:

- Clone Skywater-pdk and the specified STD_CELL_LIBRARY, SPECIAL_VOLTAGE_LIBRARY, and IO_LIBRARY and build it.

- Clone open_pdks and set up the pdk for OpenLANE use.

- Pull the OpenLANE docker container.

- Test the whole setup with a complete run on a small design

spm.

-

the default STD_CELL_LIBRARY is sky130_fd_sc_hd. You can change that by running:

export STD_CELL_LIBRARY=<Library name, i.e. sky130_fd_sc_ls>-

Other options are:

- sky130_fd_sc_hs

- sky130_fd_sc_ms

- sky130_fd_sc_ls

- sky130_fd_sc_hdll

-

You can install the full pdk by running

make full-pdkinstead ofmake pdk -

You can install the pdk manually -outside of the Makefile- by following the instructions provided here.

-

Refer to this for more details on the structure.

-

For curious users: For more details about the docker container and its process, the following instructions walk you through the process of using docker containers to build the needed tools then integrate them into OpenLANE flow. You Don't Need To Re-Build It.

If you already have the repo locally, then no need to re-clone it. You can directly run the following:

cd openlane/

git checkout master

git pull

export PDK_ROOT=<absolute path to where skywater-pdk and open_pdks will reside>

make openlane

make pdk

make test # This is to test that the flow and the pdk were properly installedThis should install the latest openlane docker container, and re-install the pdk for the latest used version.

DISCLAIMER: This sub-section is to give you an understanding of what happens under the hood in the Makefile. You don't need to run the instructions here, if you already ran make openlane

To setup openlane you can pull the docker container following these instructions:

git clone https://github.com/efabless/openlane.git

docker pull efabless/openlane:currentYou have one of two options:

The easiest way to mount the proper directories into the docker container would be to rely on the Makefile:

make mount- Note:

- Default PDK_ROOT is

$(pwd)/pdks. If you have installed the PDK at a different location, run the following beforemake mount:export PDK_ROOT=<absolute path to where skywater-pdk, open_pdks, and sky130A reside>

- Default IMAGE_NAME is efabless/openlane:current. If you want to use a different version, run the following before

make mount:export IMAGE_NAME=<docker image name>

- Default PDK_ROOT is

The following is roughly what happens under the hood when you run make mount + the required exports:

export PDK_ROOT=<absolute path to where skywater-pdk and open_pdks will reside>

export IMAGE_NAME=<docker image name>

docker run -it -v $(pwd):/openLANE_flow -v $PDK_ROOT:$PDK_ROOT -e PDK_ROOT=$PDK_ROOT -u $(id -u $USER):$(id -g $USER) $IMAGE_NAMENote: this will mount the openlane directory and the pdk root inside the container.

Use the following example to check the overall setup:

./flow.tcl -design spmTo run OpenLANE on multiple designs at the same time, check this section.

Having trouble running the flow? check FAQs

The following are arguments that can be passed to flow.tcl

| Argument | Description |

|---|---|

-design <folder path> (Required) |

Specifies the design folder. A design folder should contain a config.tcl defining the design parameters. If the folder is not found, ./designs directory is searched |

-config_file <file> (Optional) |

Specifies the design's configuration file for running the flow. For example, to run the flow using /spm/config2.tcl Use run ./flow.tcl -design /spm -config_file /spm/config2.tcl By default config.tcl is used.

|

-config_tag <name> (Optional) |

Specifies the design's configuration file for running the flow. For example, to run the flow using designs/spm/config2.tcl Use run ./flow.tcl -design spm -config_tag config2 By default config is used.

|

-tag <name> (Optional) |

Specifies a name for a specific run. If the tag is not specified, a timestamp is generated for identification of that run. Can Specify the configuration file name in case of using -init_design_config

|

-run_path <path> (Optional) |

Specifies a path to save the run in. By default the run is in design_path/, where the design path is the one passed to -design

|

-save |

A flag to save a runs results like .mag and .lef in the design's folder |

-save_path <path> (Optional) |

Specifies a different path to save the design's result. This options is to be used with the -save flag

|

-src <verilog_source_file> (Optional) |

Sets the verilog source code file(s) in case of using `-init_design_config`. The default is that the source code files are under design_path/src/, where the design path is the one passed to -design

|

-init_design_config (Optional) |

Creates a tcl configuration file for a design. -tag <name> can be added to rename the config file to <name>.tcl

|

-overwrite (Optional) |

Flag to overwirte an existing run with the same tag |

-interactive (Optional) |

Flag to run openlane flow in interactive mode |

-file <file_path> (Optional) |

Passes a script of interactive commands in interactive mode |

-synth_explore (Boolean) |

If enabled, synthesis exploration will be run (only synthesis exploration), which will try out the available synthesis strategies against the input design. The output will be the four possible gate level netlists under <run_path/results/synthesis> and a summary report under reports that compares the 4 outputs. |

-lvs (Boolean) |

If enabled, only LVS will be run on the design. in which case the user must also pass: -design DESIGN_DIR -gds DESIGN_GDS -net DESIGN_NETLIST. |

-drc (Boolean) |

If enabled, only DRC will be run on the design. in which case the user must also pass: -design DESIGN_DIR -gds DESIGN_GDS -report OUTPUT_REPORT_PATH -magicrc MAGICRC. |

To add a new design, follow the instructions provided here

This file also includes useful information about the design configuration files. It also includes useful utilities for exploring and updating design configurations for each (PDK,STD_CELL_LIBRARY) pair.

|

OpenLANE flow consists of several stages. By default all flow steps are run in sequence. Each stage may consist of multiple sub-stages. OpenLANE can also be run interactively as shown here.

- Synthesis

yosys- Performs RTL synthesisabc- Performs technology mappingOpenSTA- Pefroms static timing analysis on the resulting netlist to generate timing reports

- Floorplan and PDN

init_fp- Defines the core area for the macro as well as the rows (used for placement) and the tracks (used for routing)ioplacer- Places the macro input and output portspdn- Generates the power distribution networktapcell- Inserts welltap and decap cells in the floorplan

- Placement

RePLace- Performs global placementResizer- Performs optional optimizations on the designOpenPhySyn- Performs timing optimizations on the designOpenDP- Perfroms detailed placement to legalize the globally placed components

- CTS

TritonCTS- Synthesizes the clock distribution network (the clock tree)

- Routing

FastRoute- Performs global routing to generate a guide file for the detailed routerCU-GR- Another option for performing global routing.TritonRoute- Performs detailed routingSPEF-Extractor- Performs SPEF extraction

- GDSII Generation

Magic- Streams out the final GDSII layout file from the routed defKlayout- Streams out the final GDSII layout file from the routed def as a back-up

- Checks

Magic- Performs DRC Checks & Antenna ChecksKlayout- Performs DRC ChecksNetgen- Performs LVS ChecksCVC- Performs Circuit Validity Checks

OpenLANE integrated several key open source tools over the execution stages:

- RTL Synthesis, Technology Mapping, and Formal Verification : yosys + abc

- Static Timing Analysis: OpenSTA

- Floor Planning: init_fp, ioPlacer, pdn and tapcell

- Placement: RePLace (Global), Resizer and OpenPhySyn (Optimizations), and OpenDP (Detailed)

- Clock Tree Synthesis: TritonCTS

- Fill Insertion: OpenDP/filler_placement

- Routing: FastRoute or CU-GR (Global) and TritonRoute (Detailed)

- SPEF Extraction: SPEF-Extractor

- GDSII Streaming out: Magic and Klayout

- DRC Checks: Magic and Klayout

- LVS check: Netgen

- Antenna Checks: Magic

- Circuit Validity Checker: CVC

All output run data is placed by default under ./designs/design_name/runs. Each flow cycle will output timestamp-marked foler containing the following file structure:

designs/<design_name>

├── config.tcl

├── runs

│ ├── <tag>

│ │ ├── config.tcl

│ │ ├── logs

│ │ │ ├── cts

│ │ │ ├── cvc

│ │ │ ├── floorplan

│ │ │ ├── klayout

│ │ │ ├── magic

│ │ │ ├── placement

│ │ │ ├── routing

│ │ │ └── synthesis

│ │ ├── reports

│ │ │ ├── cts

│ │ │ ├── cvc

│ │ │ ├── floorplan

│ │ │ ├── klayout

│ │ │ ├── magic

│ │ │ ├── placement

│ │ │ ├── routing

│ │ │ └── synthesis

│ │ ├── results

│ │ │ ├── cts

│ │ │ ├── cvc

│ │ │ ├── floorplan

│ │ │ ├── klayout

│ │ │ ├── magic

│ │ │ ├── placement

│ │ │ ├── routing

│ │ │ └── synthesis

│ │ └── tmp

│ │ ├── cts

│ │ ├── cvc

│ │ ├── floorplan

│ │ ├── klayout

│ │ ├── magic

│ │ ├── placement

│ │ ├── routing

│ │ └── synthesis

To delete all generated runs under all designs:

- inside the docker container:

./clean_runs.tcl

- outside the docker container:

make clean_runs

- PDK / technology specific

- Flow specific

- Design specific

-

A PDK should define at least one standard cell library(SCL) for the PDK. A common configuration file for all SCLs is located in:

$PDK_ROOT/$PDK/config.tcl-

Sometimes the PDK comes with several standard cell libraries. Each has an own configuration file that defines extra variables specific to the SCL. It may also override variables in the common PDK configuration file which is located in:

$PDK_ROOT/$PDK/$STD_CELL_LIBRARY/config.tcl -

More on configuring a new PDK in this section

-

-

Flow specific variables are related to the flow and are initialized with default values in:

./configuration/ -

Finally, each design should have it's own configuration file with some required variables which are available in this list. A design configuration file may override any of the variables defined in PDK or flow configuration files. This is the global configurations for the design:

./designs/<design>/config.tcl- More on design configurations in here

A list of all available variables can be found here.

As mentioned earlier, everytime a new design or a new (PDK,STD_CELL_LIBRARY) pair is added, or any update happens in the flow tools, a re-configuration for the designs is needed. The reconfiguration is methodical and so an exploration script was developed to aid the designer in reconfiguring his designs if needed. As explained here that each design has multiple configuration files for each (PDK,STD_CELL_LIBRARY) pair.

OpenLANE provides run_designs.py, a script that can do multiple runs in a parallel using different configurations. A run consists of a set of designs and a configuration file that contains the configuration values. It is useful to explore the design implementation using different configurations to figure out the best one(s).

Also, it can be used for testing the flow by running the flow against several designs using their best configurations. For example the following run: spm using its default configuration files config.tcl. :

python3 run_designs.py --designs spm xtea md5 aes256 --tag test --threads 3

For more information on how to run this script, refer to this file

For more information on design configurations, how to update them, and the need for an exploration for each design, refer to this file

This is discussed in more detail here.

The first step of chip integration is hardening the macros. To learn more about this check this file.

Using openlane, you can produce a GDSII from a chip RTL. This is done by applying a certain methodology that we follow using our custom scripts and the integrated tools.

To learn more about Chip Integration. Check this file

To get a full list of the openlane commands, first introduce yourself to the interactive mode of openlane here. Then check the full documentation of the OpenLANE commands here.

The full documentation of OpenLANE run configurations could be found here.

We discuss the details of how to contribute to OpenLANE in this documentation.

To check the original author list of OpenLANE, check this.

- Ahmed Ghazy and Mohamed Shalan, "OpenLane: The Open-Source Digital ASIC Implementation Flow", Article No.21, Workshop on Open-Source EDA Technology (WOSET), 2020. Paper

- M. Shalan and T. Edwards, "Building OpenLANE: A 130nm OpenROAD-based Tapeout- Proven Flow : Invited Paper," 2020 IEEE/ACM International Conference On Computer Aided Design (ICCAD), San Diego, CA, USA, 2020, pp. 1-6.

- R. Timothy Edwards, M. Shalan and M. Kassem, "Real Silicon using Open Source EDA," in IEEE Design & Test, doi: 10.1109/MDAT.2021.3050000.

- FOSSi Dial-Up - OpenLane, A Digital ASIC Flow for SkyWater 130nm Open PDK, Mohamed Shalan

- Openlane Overview, Ahmed Ghazy

- Free VLSI Tutorial - VSD - A complete guide to install Openlane and Sky130nm PDK

- Sky130 - Exploring OpenLANE and OpenDB to create a register file , Sylvain Munaut

- VLSI SoC EDA openLANE with Skywater 130 PDK, Gary Huang