awesome-CXL

Contents

Quick Intro

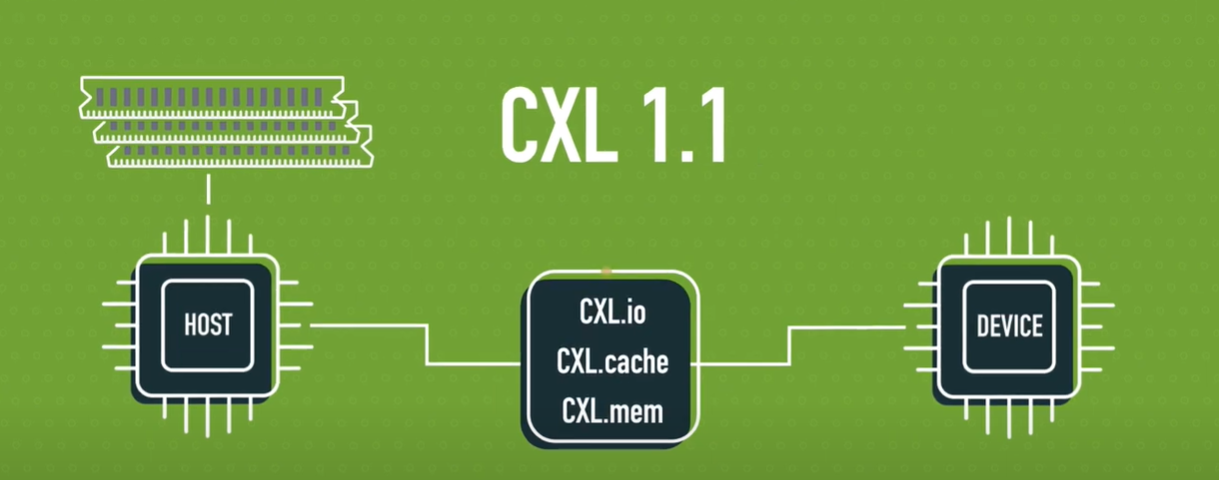

- 3 min video about CXL: Introduction to Compute Express Link™ (CXL™) Technology

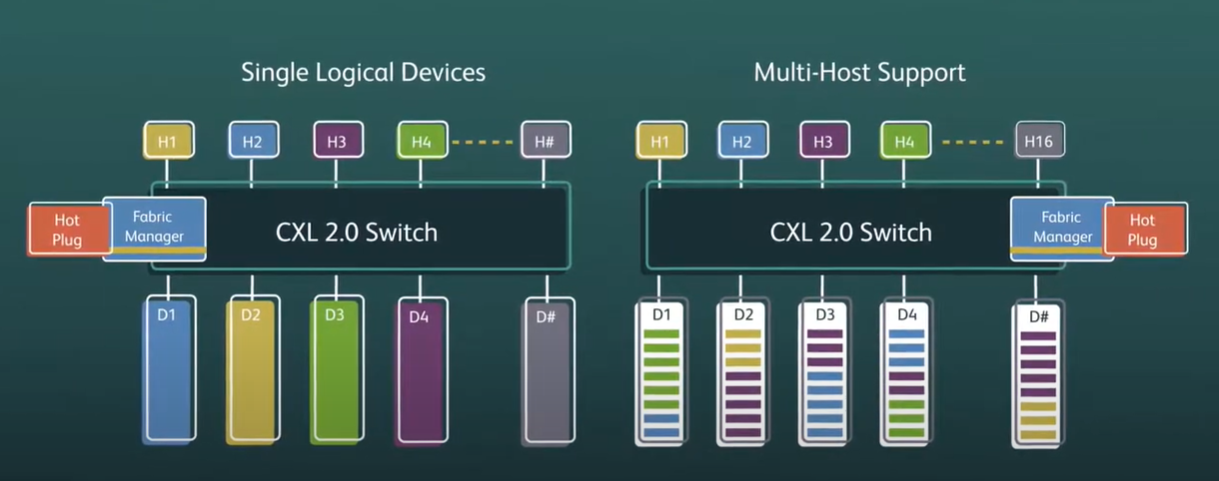

- 2 min video about CXL 2.0: CXL™ 2.0 Overview

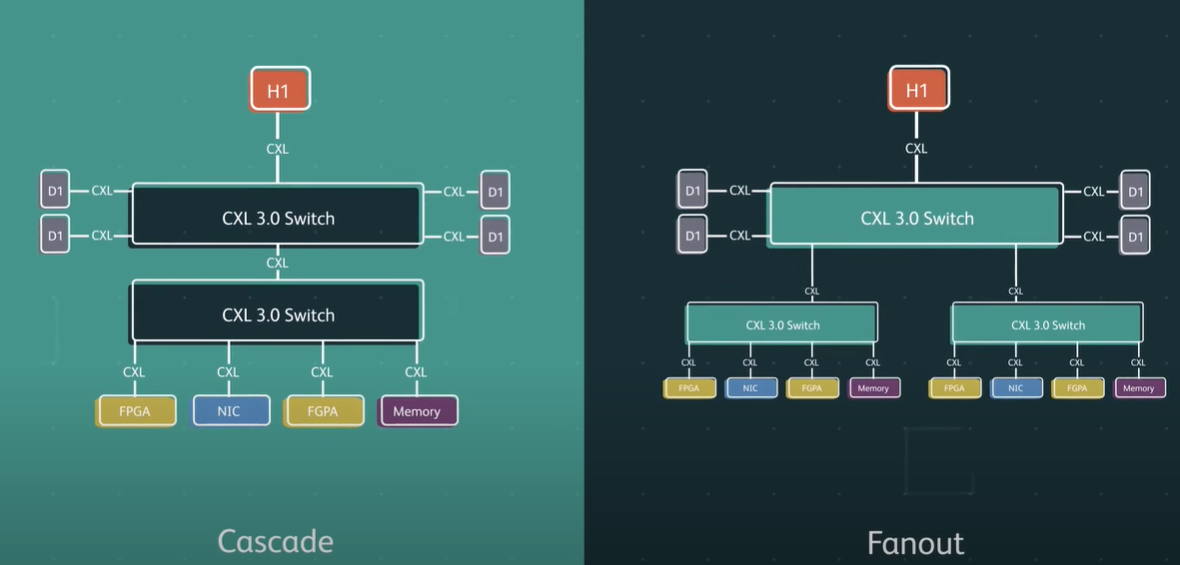

- 3 min video about CXL 3.0: Introducing Compute Express Link™ (CXL™) 3.0

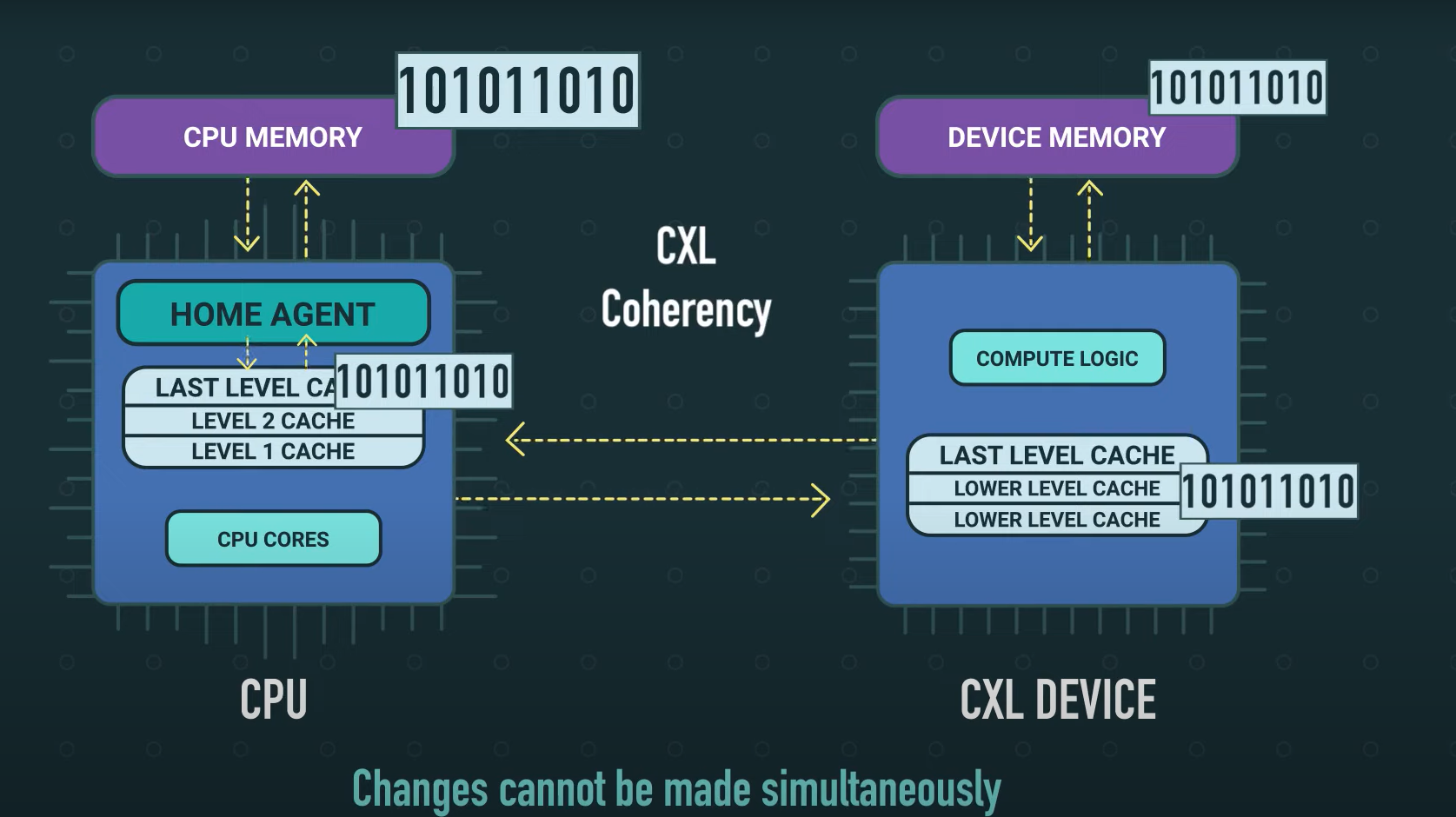

- 3 min video about CXL Cache Coherency: Exploring Compute Express Link™ (CXL™) Cache Coherency

Webinars and tutorials

CXL insights from the industry

3 Jan 2023, SDC 2022

- Contents:

- Architecture and variety of memory services that will be available to developers with the advent of CXL

- The different ways that developers will be able to access the memory services

- Examples of memory service APIs and how to use them

- Presented By: Charles Fan, MemVerge

- Recording: SDC2022 – Memory Disaggregation and Pooling with CXL

3 Dec 2022, HotChips 34

- Contents:

- CXL overview and evolution

- CXL2/CXL3 coherency deep dive

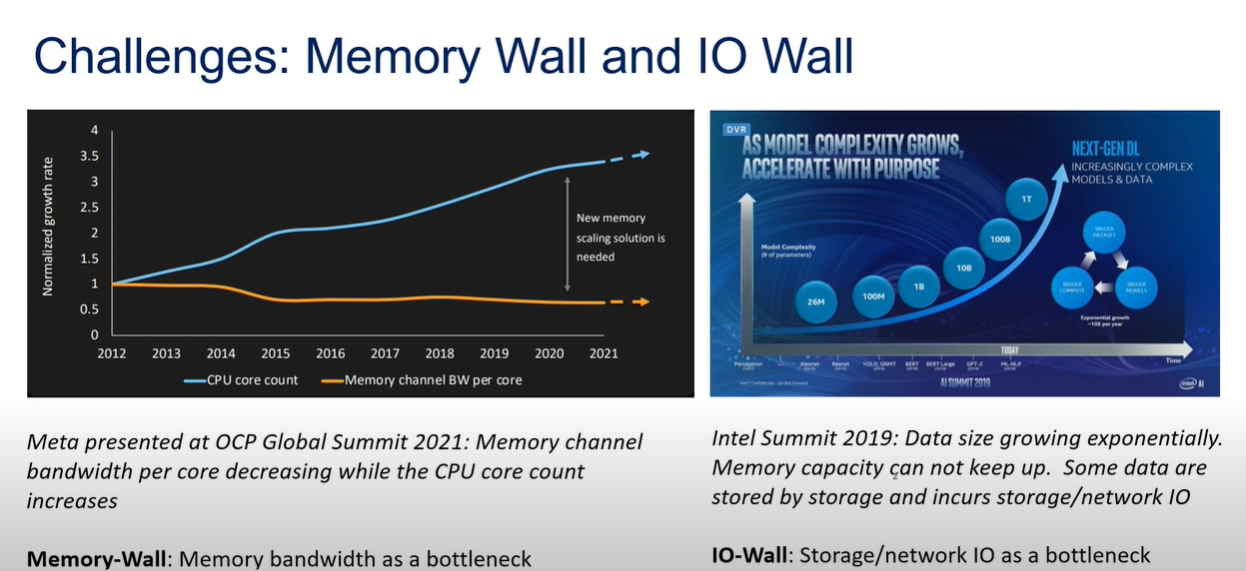

- Memory use cases and challenges

- CXL3 Fabric introduction & use cases

- Presented By: Ishwar Agarwal, Robert Blankenship(Intel); Prakash Chauhan, Meta, Mahesh Wagh, Tony Brewer, Micron, and Nathan Kalyanasundharam(AMD)

- Recording: HC34-T1: CXL

- Slides: Hot Chips 34

Papers and news

8 - 10 August, 2023

- Event: Flash Memory Summit

- Presentations:

July 11, 2023, ATC 2023

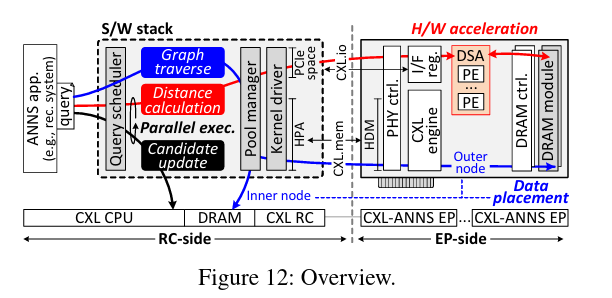

- Paper: CXL-ANNS: Software-Hardware Collaborative Memory Disaggregation and Computation for Billion-Scale Approximate Nearest Neighbor Search

- Authors: Junhyeok Jang, Computer Architecture and Memory Systems Laboratory, KAIST; Hanjin Choi, Computer Architecture and Memory Systems Laboratory, KAIST and Panmnesia, Inc.; Hanyeoreum Bae and Seungjun Lee, Computer Architecture and Memory Systems Laboratory, KAIST; Miryeong Kwon and Myoungsoo Jung, Computer Architecture and Memory Systems Laboratory, KAIST and Panmnesia, Inc.

July 11, 2023, ATC 2023

- Paper: Overcoming the Memory Wall with CXL-Enabled SSDs

- Authors: Shao-Peng Yang, Syracuse University; Minjae Kim, DGIST; Sanghyun Nam, Soongsil University; Juhyung Park, DGIST; Jin-yong Choi and Eyee Hyun Nam, FADU Inc.; Eunji Lee, Soongsil University; Sungjin Lee, DGIST; Bryan S. Kim, Syracuse University

12 May 2023, DRAM supporting CXL 2.0

Samsung Develops Industry’s First CXL DRAM Supporting CXL 2.0! See more details here

Building on its development of the industry’s first CXL 1.1-based CXL DRAM in May of 2022, Samsung’s introduction of the 128GB CXL DRAM based on CXL 2.0 is expected to accelerate commercialization of next-generation memory solutions. The new CXL DRAM supports PCle 5.0 interface (x8 lanes) and provides bandwidth of up to 35GB per second.

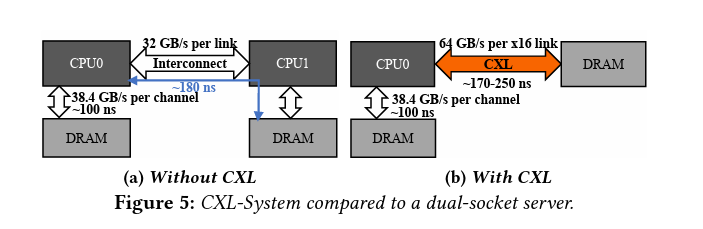

27 March 2023, CXL 1.1

- Paper: Demystifying CXL Memory with Genuine CXL-Ready Systems and Devices

- Authors: Yan Sun and Yifan Yuan and Zeduo Yu and Reese Kuper and Ipoom Jeong and Ren Wang and Nam Sung Kim

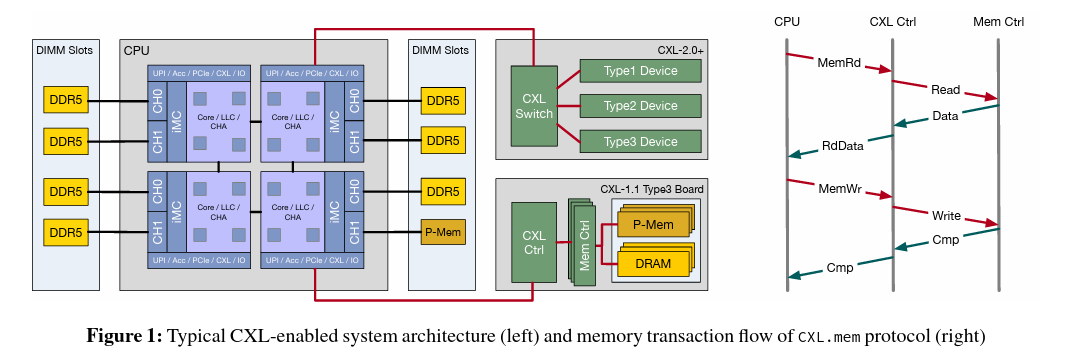

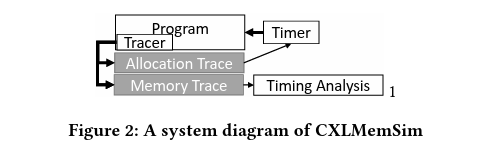

10 Mar 2023, Software Simulated CXL

- Paper: CXLMemSim: A pure software simulated CXL.mem for performance characterization

- Authors: Yiwei Yang and Pooneh Safayenikoo and Jiacheng Ma and Tanvir Ahmed Khan and Andrew Quinn

- Presentation: CXLMemSim: A pure software simulated CXL.mem for performance characterization #92

- source code: CXL.mem Simulator

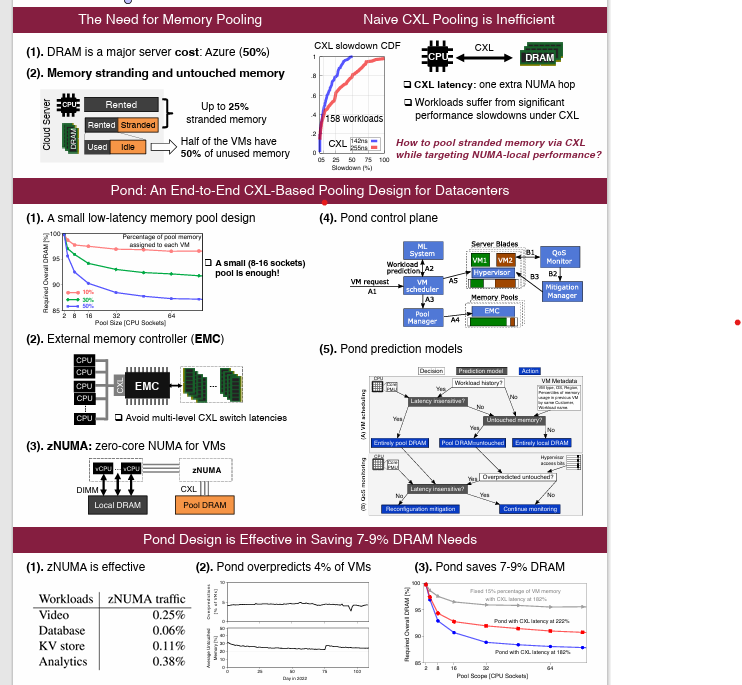

30 January 2023, ASPLOS 2023

- Paper: Pond: CXL-Based Memory Pooling Systems for Cloud Platforms

- Authors: Li, Huaicheng and Berger, Daniel S. and Hsu, Lisa and Ernst, Daniel and Zardoshti, Pantea and Novakovic, Stanko and Shah, Monish and Rajadnya, Samir and Lee, Scott and Agarwal, Ishwar and Hill, Mark D. and Fontoura, Marcus and Bianchini, Ricardo

- Presentation: ASPLOS'23 - Session 9A - Pond: CXL-Based Memory Pooling Systems for Cloud Platforms

- source code: Pond - Compute Express Link (CXL) based Memory Pooling Systems

25 March 2023, ASPLOS 2023

- Paper: TPP: Transparent Page Placement for CXL-Enabled Tiered-Memory

- Authors: Maruf, Hasan Al and Wang, Hao and Dhanotia, Abhishek and Weiner, Johannes and Agarwal, Niket and Bhattacharya, Pallab and Petersen, Chris and Chowdhury, Mosharaf and Kanaujia, Shobhit and Chauhan, Prakash

- Presentation: ASPLOS'23 - Session 9A - TPP: Transparent Page Placement for CXL-Enabled Tiered Memory

- source code: [PATCH 5/5] Transparent Page Placement for Tiered-Memory

21 October 2022, USENIX ATC 2022, CXL 2.0 based on FPGA

- Paper: Direct Access, High-Performance Memory Disaggregation with DirectCXL

- Authors: Donghyun Gouk and Sangwon Lee and Miryeong Kwon and Myoungsoo Jung

- Presentation: USENIX ATC '22 - Direct Access, High-Performance Memory Disaggregation with DirectCXL

27 June 2022, HotStorage 2022

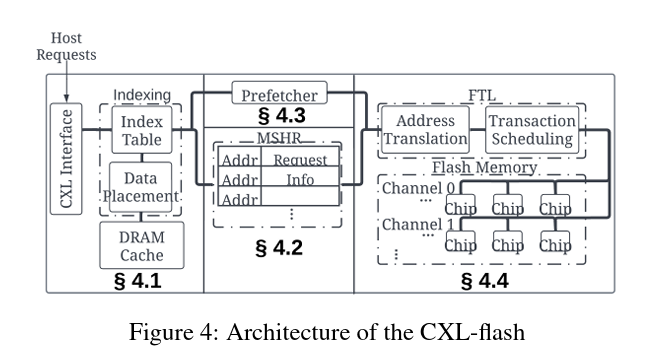

- Paper: Hello bytes, bye blocks: PCIe storage meets compute express link for memory expansion (CXL-SSD)

- Authors: Jung, Myoungsoo

- Presentation: CAMEL | CXL-SSD: Expanding PCIe Storage as Working Memory over CXL