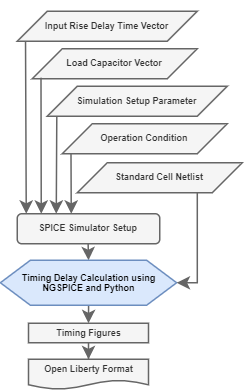

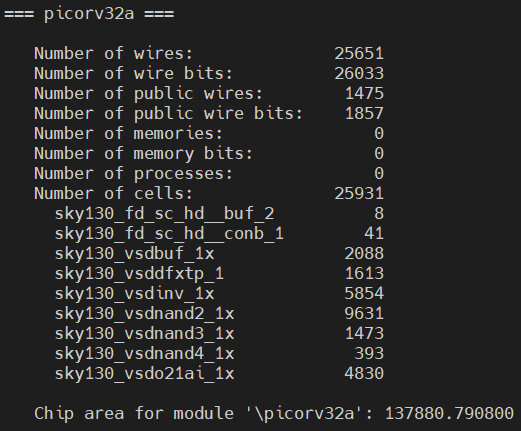

In this repository, simplified scripts for doing the characterization of a standard cell are presented. The approach shown here is based on Non-linear models of cell delay and power dissipation. A cell layout library was developed, and a project named picorv32a synthesized using the OpenLane tool with the liberty file build by the scripts to prove the suitability of the approach.

- Standard Cell Characterizer for Skywater 130nm PDK - Under Development

Cell Characterization is the process of simulating circuits with a fitting harness(stimulus) to measure parameters, accompanied by organizing measured data into a formatted file structure known as liberty.The parameter measurement is done to describe the performance of the cell.

The parameters could be related to any of the following:

- Power - Leakage Power, Internal Power, and Switching Power.

- Timing - Delays, hold time, Setup Time, etc

- Noise - Capacitive crosstalk noise

Currently, this repository focuses only on the timing aspect of the parameter measurement.

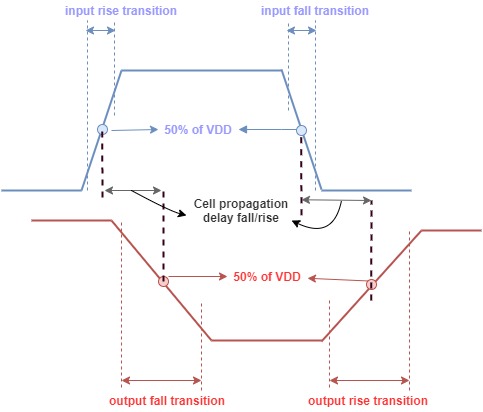

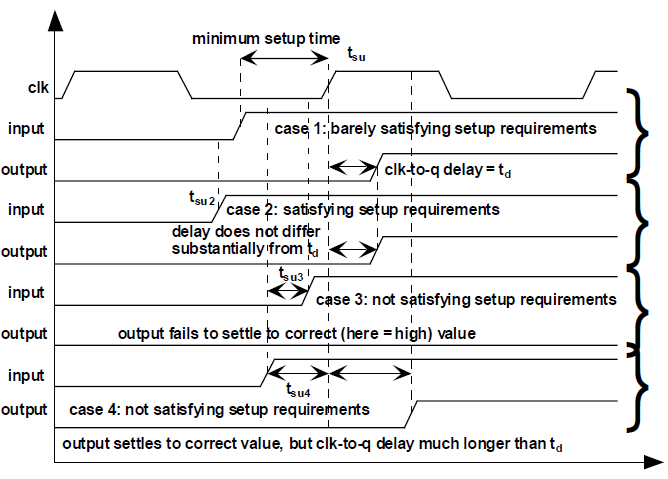

Timing Views generation involves measurement of propagation delays (between input and output), transition time, and constraints (hold, setup, removal, and recovery time). These measurement is done at a particular event and these event are generally defined in the liberty file as the threshold points.

NGSPICE Control Commands:

* Measuring Rise Transition Time @ 20-80% of VDD(1.8V)

meas tran rt1 when v(Y)=1.44 RISE=2

meas tran rt2 when v(Y)=0.36 RISE=2

let rise_tran = ((rt1-rt2)/1e-09)

* Measuring Cell Rise Time @ 50% of VDD(1.8V)

meas tran tinrise when v(A)=0.9 RISE=1

meas tran torise when v(Y)=0.9 RISE=1

let crise = (torise-tinrise)/1e-09

if abs(crise)>20

meas tran tinrise when v(A)=0.9 FALL=1

meas tran torise when v(Y)=0.9 RISE=1

let crise = abs(tinrise-torise)/1e-09

end

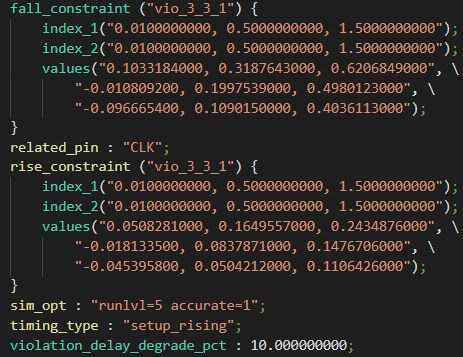

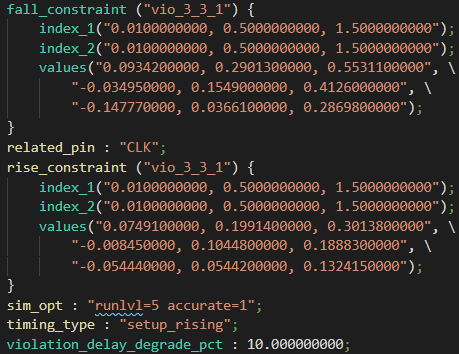

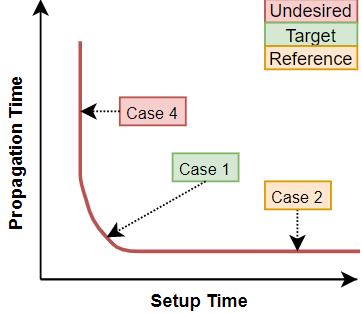

The setup-time is measured using the bisection method. In this method, the reference circuit(case 1) propagation delay(tpd) times 1.1 factor is considered as the target tpd(case 2), whereas the high tpd is assumed to be undesired(case 4).

Step 0: Perquisites based on Ubuntu OS

- Software Requirements: NGSPICE and python 3

- Numpy module download:

$ pip3 install numpy - Clone the repository:

$ git clone https://github.com/vsdip/vsdStdCellCharacterizer_sky130.git - Change Directory to timing_arch:

$ cd vsdStdCellCharacterizer_sky130 - All the commands need to be run from the root directory i.e

user_name@PC_name:~/vsdStdCellCharacterizer_sky130$

Step 1: Edit config.py

- Enter custom cell folder, spice and lef file that needs to be characterized.

- Mention input vectors for input delay and load capacitor.

- Enter Logic function.

- Enter Base Liberty File and output Liberty File

sky130_fd_sc_hd__buf_1 example: sky130_fd_sc_hd__buf_1 config.py

- Replace 'example/sky130_fd_sc_hd__buf_1/' directory with your cell working directory in config.py file.

- Similarly replace spice file name

sky130_fd_sc_hd__buf_1.spiceandsky130_fd_sc_hd__buf_1.lefwith your spice and lef file name. Make sure the spice format has the subckt inside it with proper scaling factor.

Step 2: Execute python file

Enter command into terminal: $ python3 combchar.py

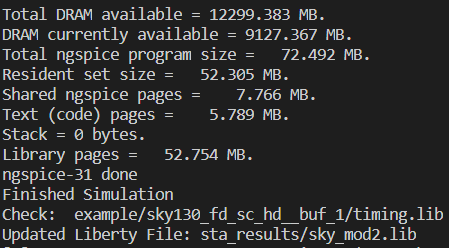

Step 3: Ideal Run Final Output:

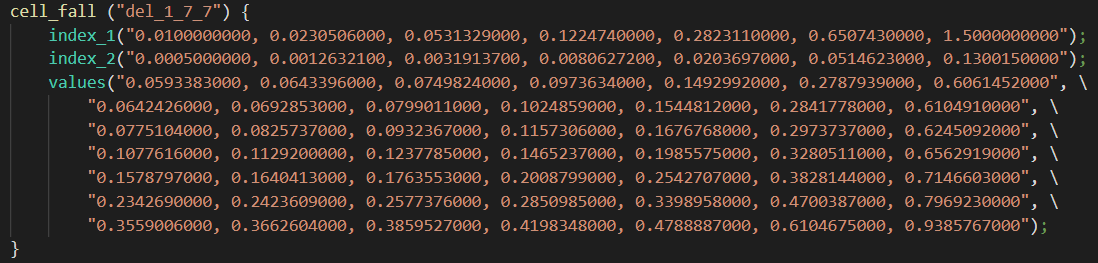

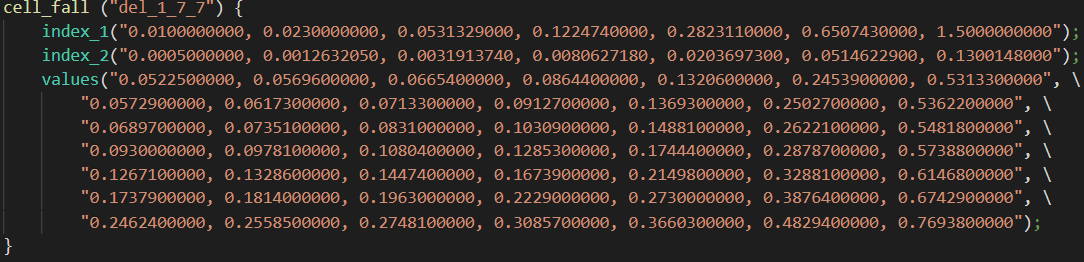

Skywater Liberty file Buf_1

Generated Liberty file Buf_1

Step 1: Edit default setting (Optional):

- Change variable under comment

Default valuesin dff.py.

Step 2: Enter inputs lef and spice file:

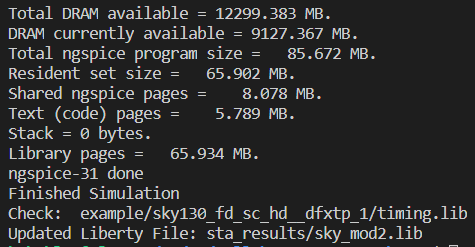

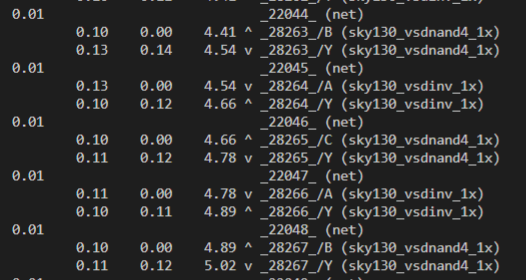

Enter command into terminal: $ python3 dff.py -lef example/sky130_fd_sc_hd__dfxtp_1/sky130_fd_sc_hd__dfxtp_1.lef -sp example/sky130_fd_sc_hd__dfxtp_1/sky130_fd_sc_hd__dfxtp_1.spice -lib sta_results/sky_mod2.lib

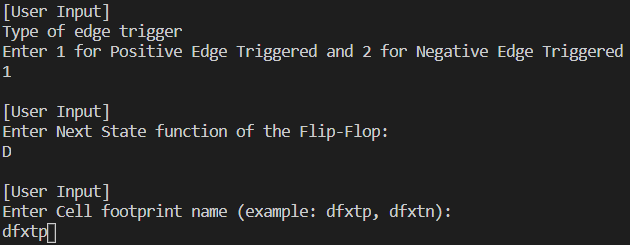

Step 3: Enter User Inputs after running the script on terminal:

Step 4: Ideal Run Final Output:

- Perquisites openSTA software. You could install using

sudo apt-get install openSTA - Change directory to sta_results:

$ cd sta_results - Replace

picorv32a.synthesis_optimized.txtfile name topicorv32a.synthesis_optimized.v - Edit the sta.conf and my_base.sdc as per your requirement.

- Run OpenSTA using command:

$ sta sta.conf. - Verify your cell of interest and make sure there is no warning due the liberty files.

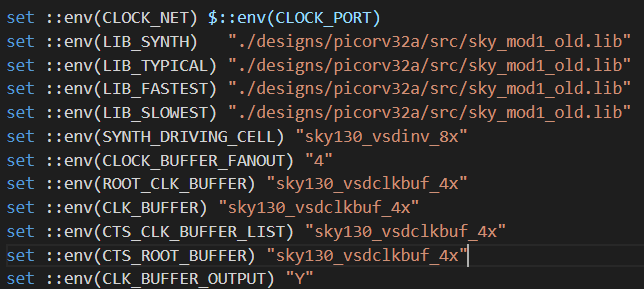

- Install OpenLane as mentioned in repo OpenLANE Built Script

- OpenLane Workshop repo for understanding openLane flow

- Skywater Library cells: sky130_fd_sc_hd__buf_2, and sky130_fd_sc_hd__conb_1.

- Custom cells: sky130_vsdbuf_1x, sky130_vsdbuf_2x, sky130_vsdclkbuf_4x, sky130_vsdinv_1x, sky130_vsdinv_8x, sky130_vsdnand2_1x, sky130_vsdnand3_1x, sky130_vsdnand4_1x, sky130_vsdo21ai_1x and sky130_vsddfxtp_1.

- Liberty File: sky_mod1.lib

- Harsh Shukla, pursuing Masters at Arizona State University

-

Kunal Ghosh, Co-founder, VSD Corp. Pvt. Ltd

-

Openlane team, Efabless corporation

- Implement tri-state and multiple output cells measurement.

- Try to generate number of timing arcs dynamically.

- Implement removal time, recovery time and minimum pulse width measurement for sequential cells.