This repo is an attempt at and a tutorial for the OpenLane Physical Design Flow

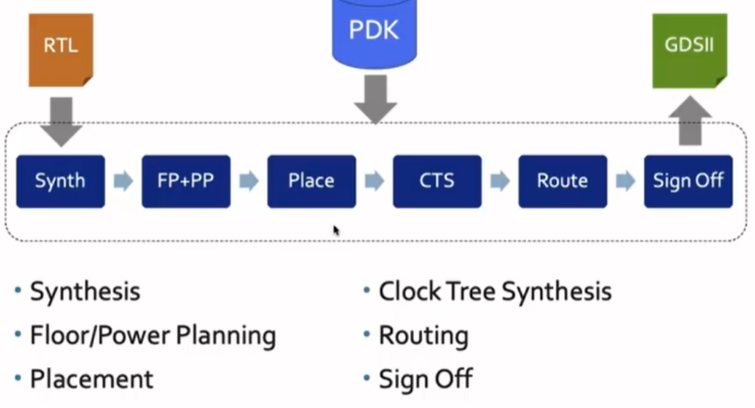

- RTL2GDS flow

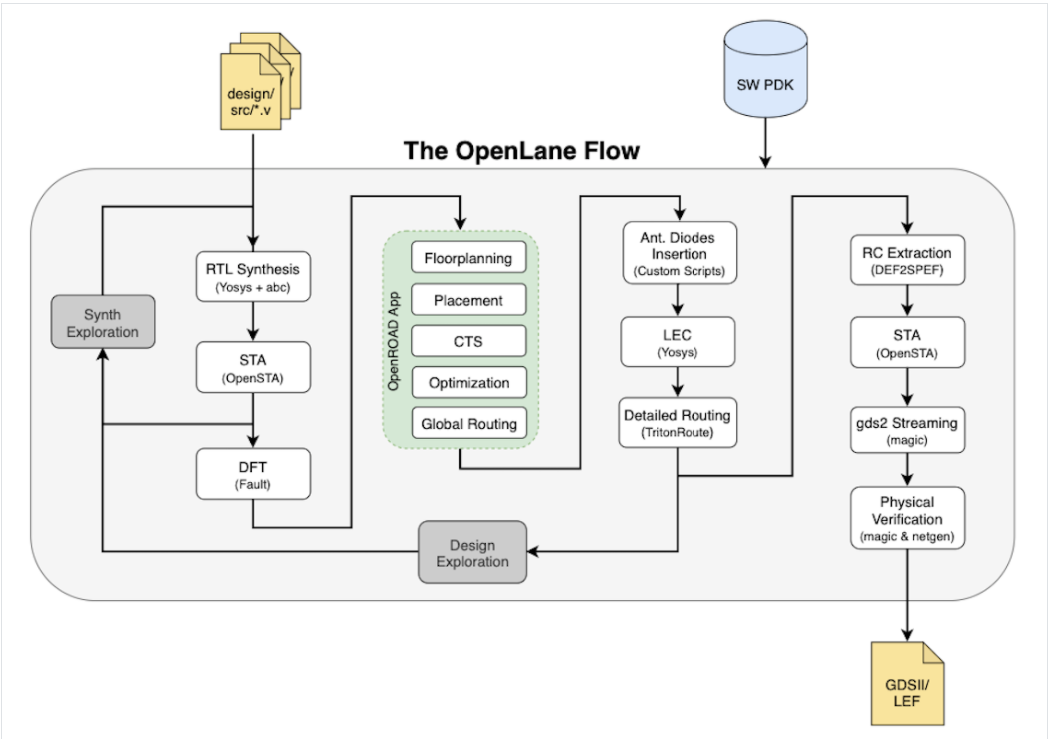

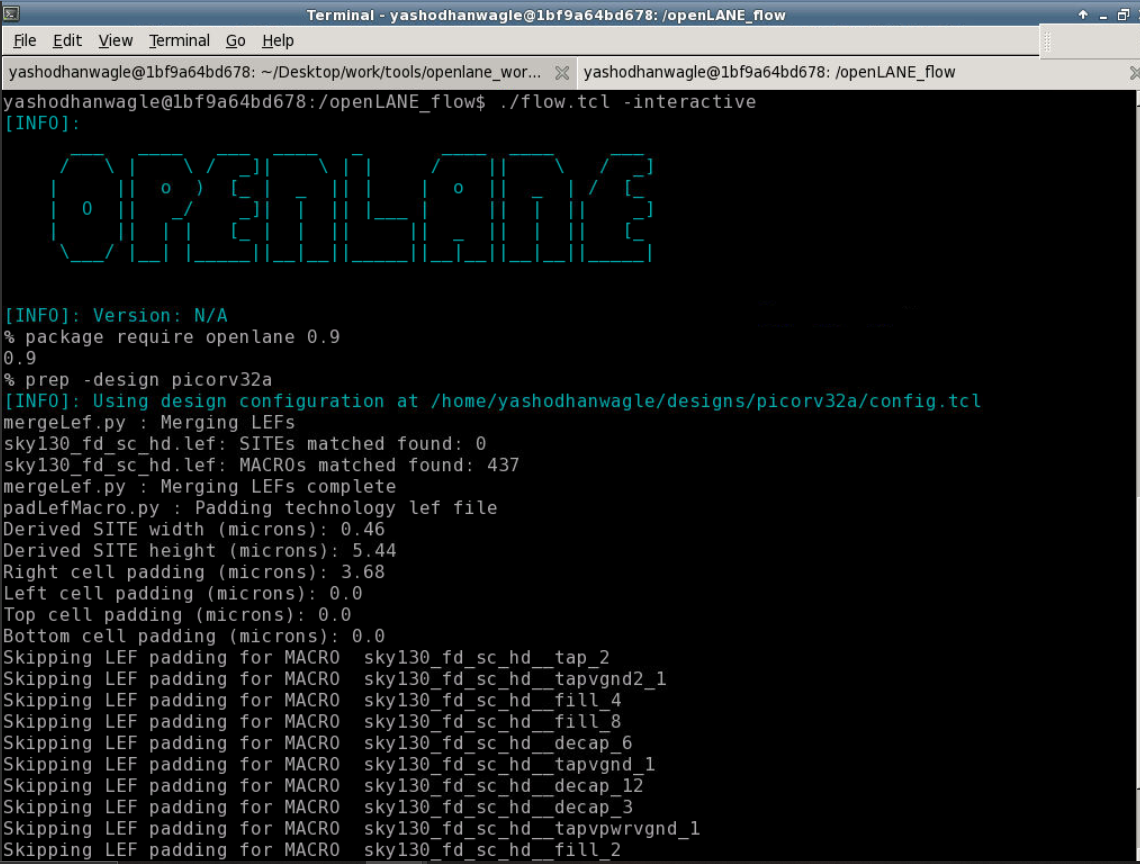

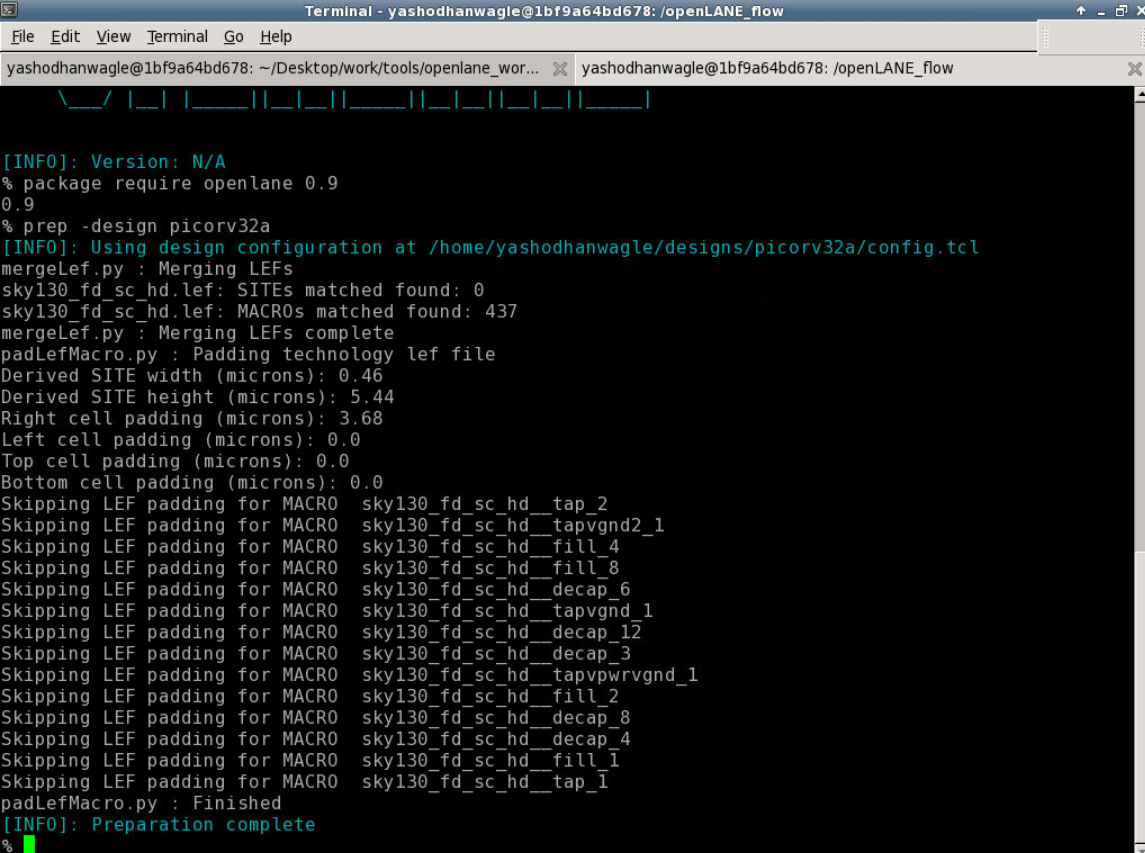

- Introduction to OpenLANE

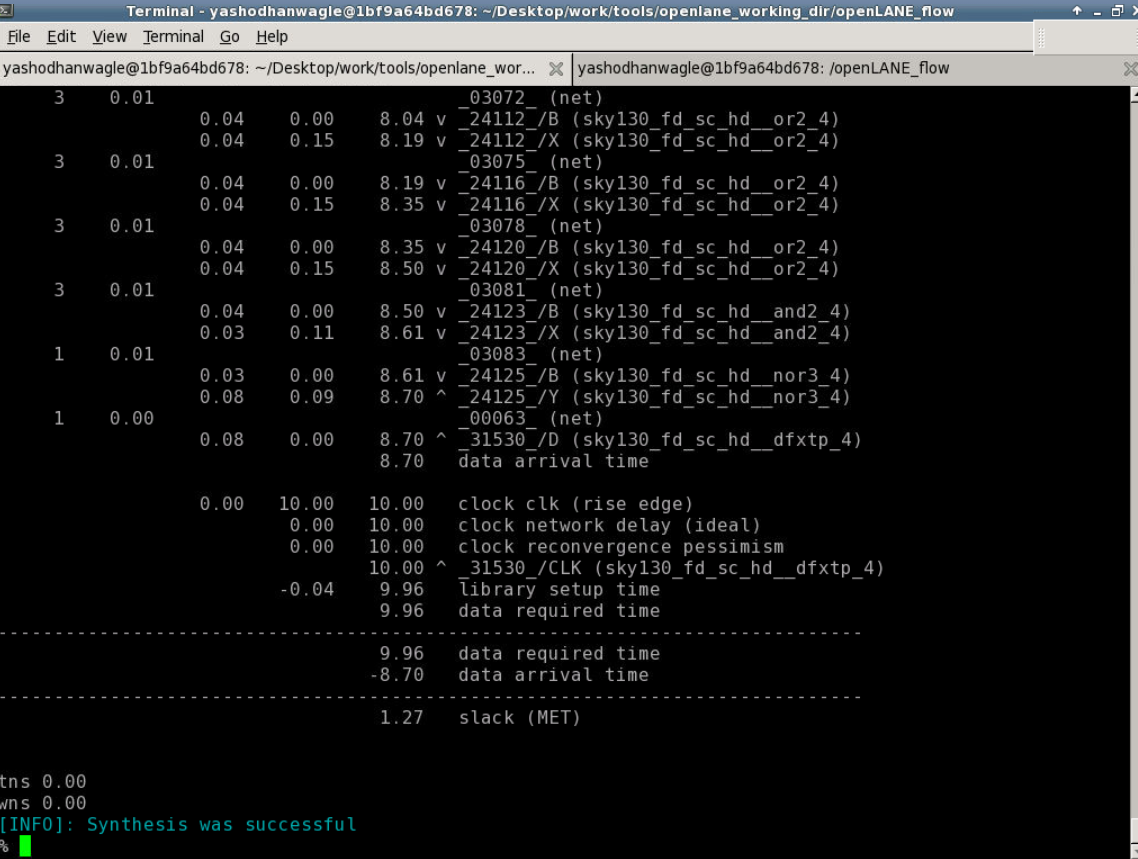

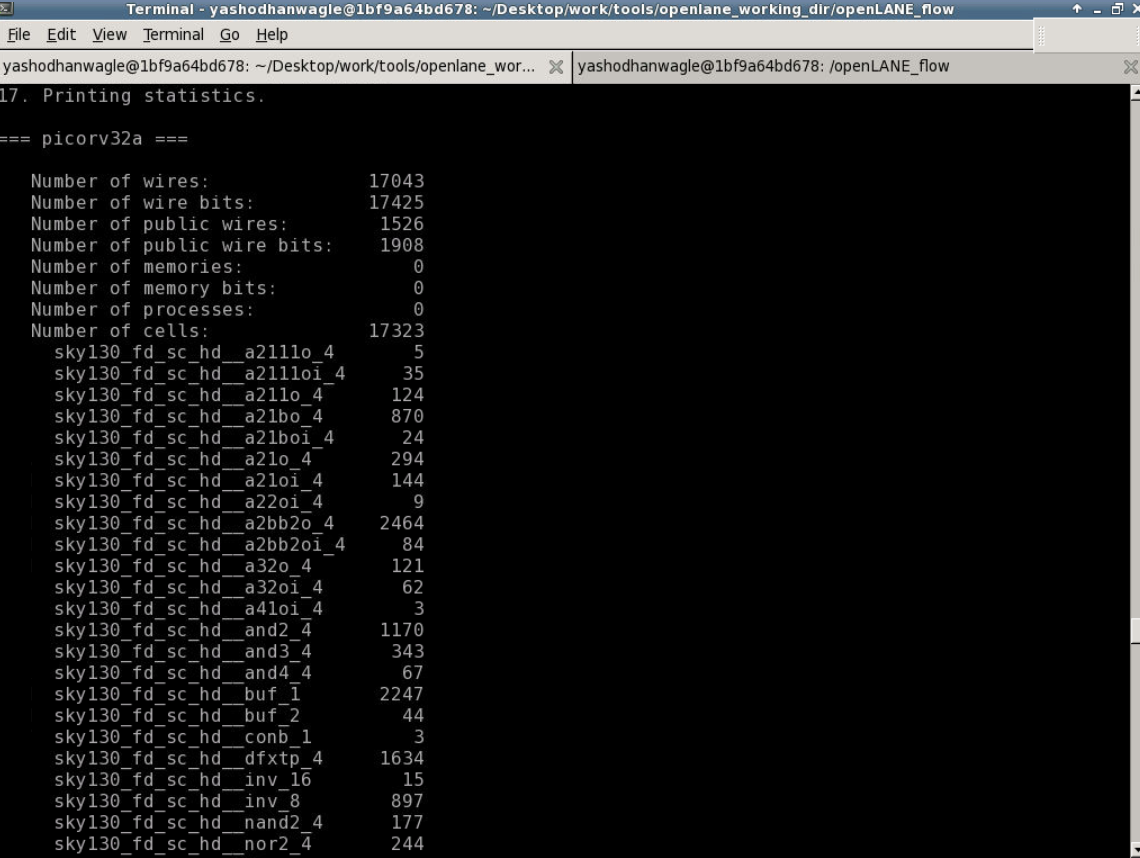

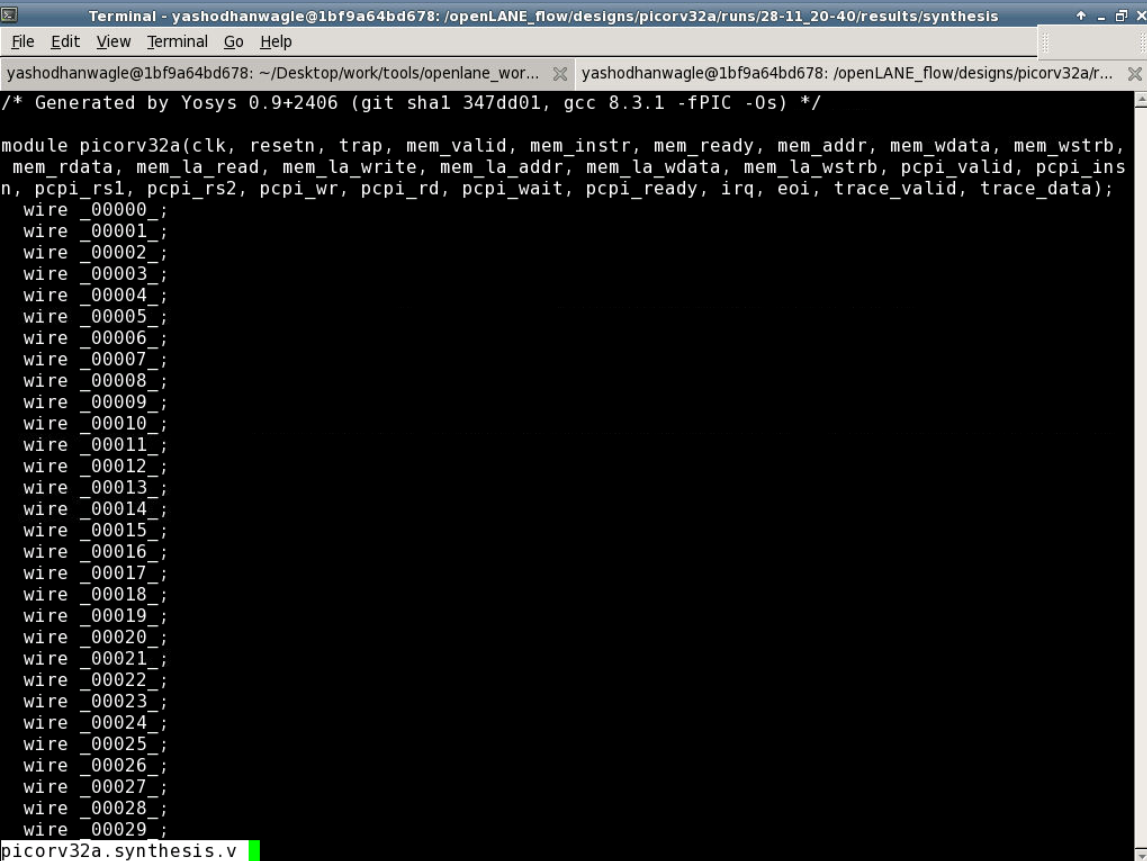

- Synthesis

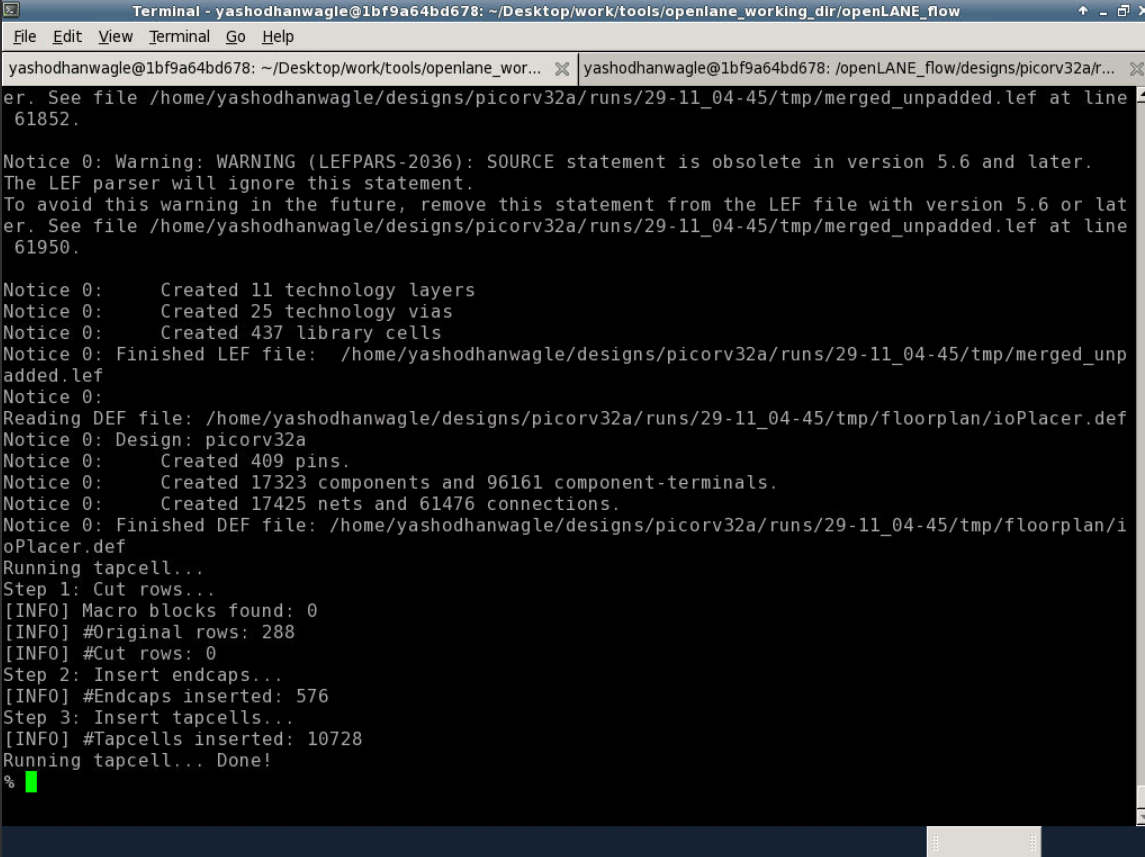

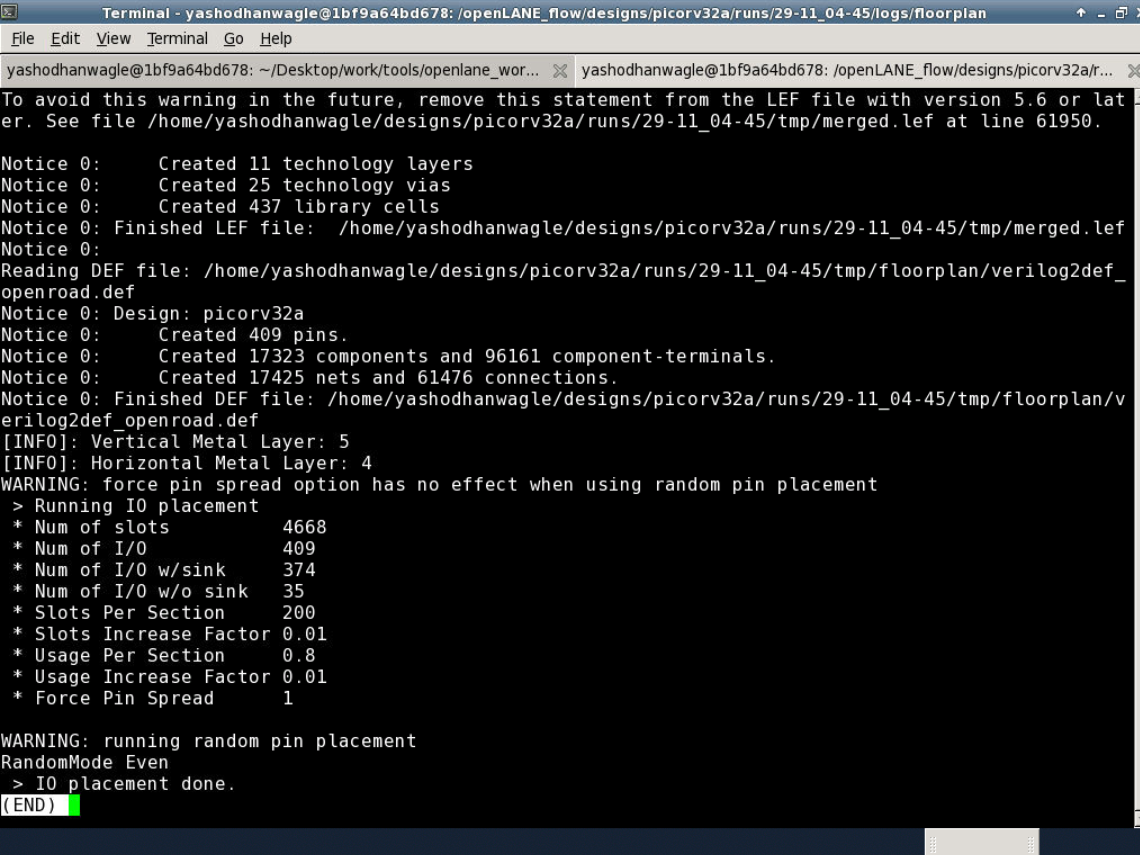

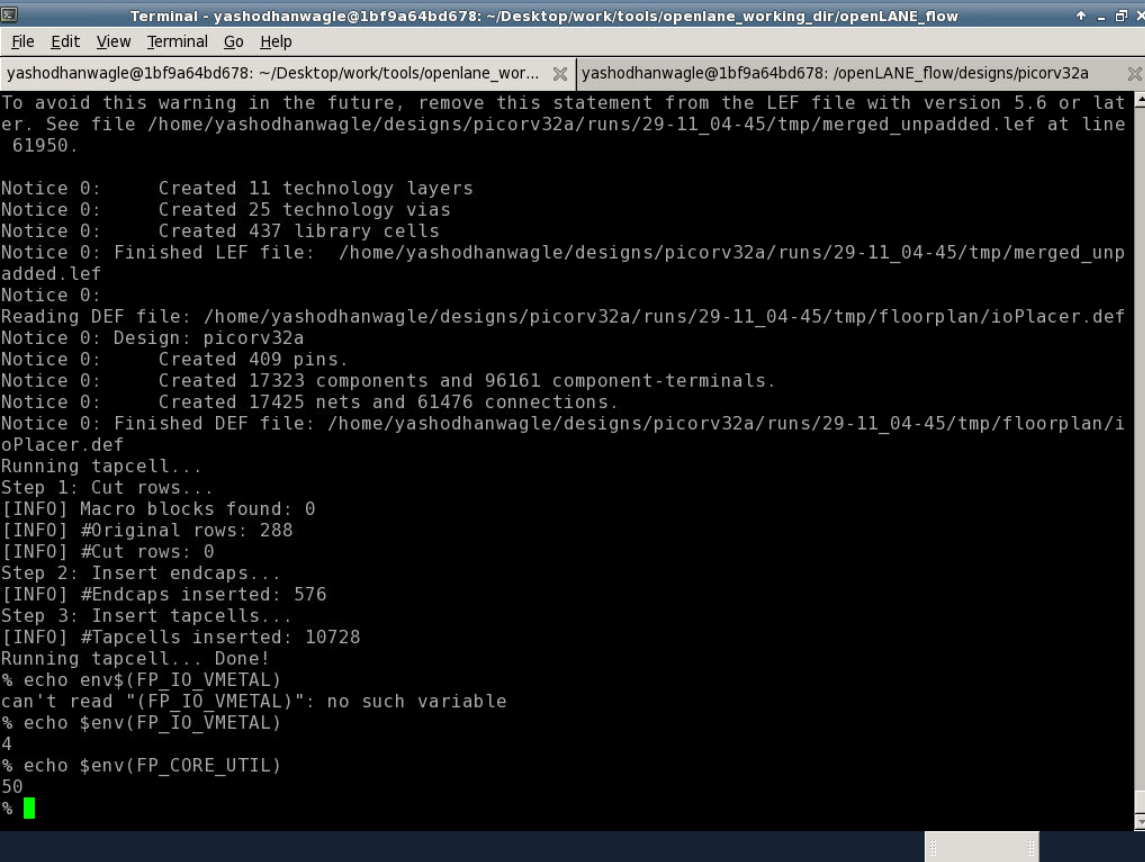

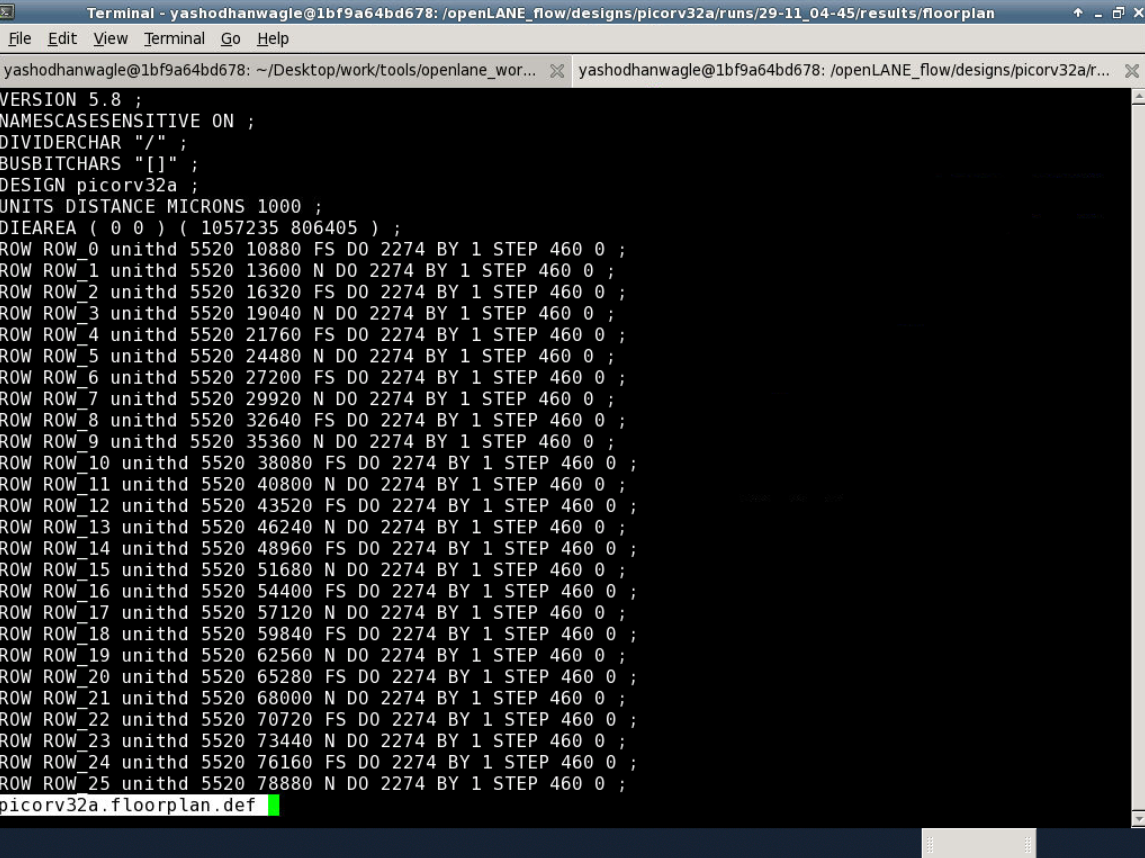

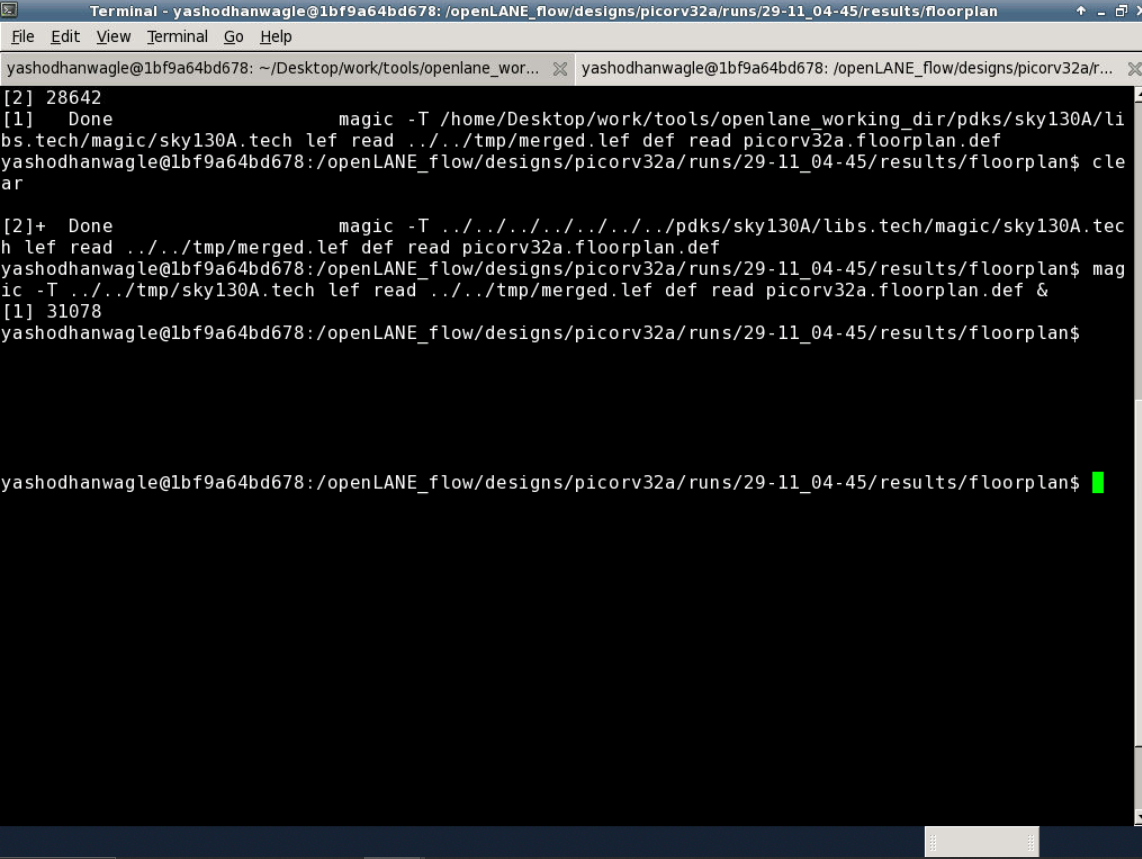

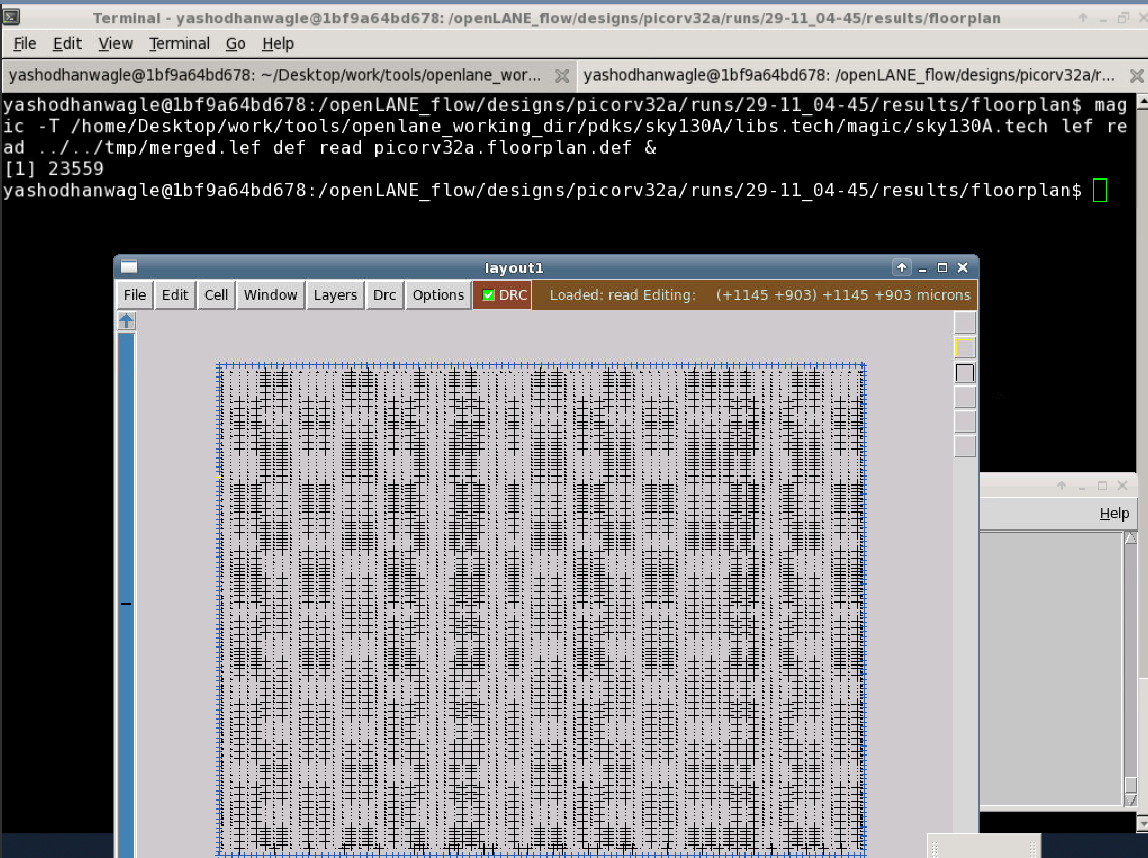

- Floorplan

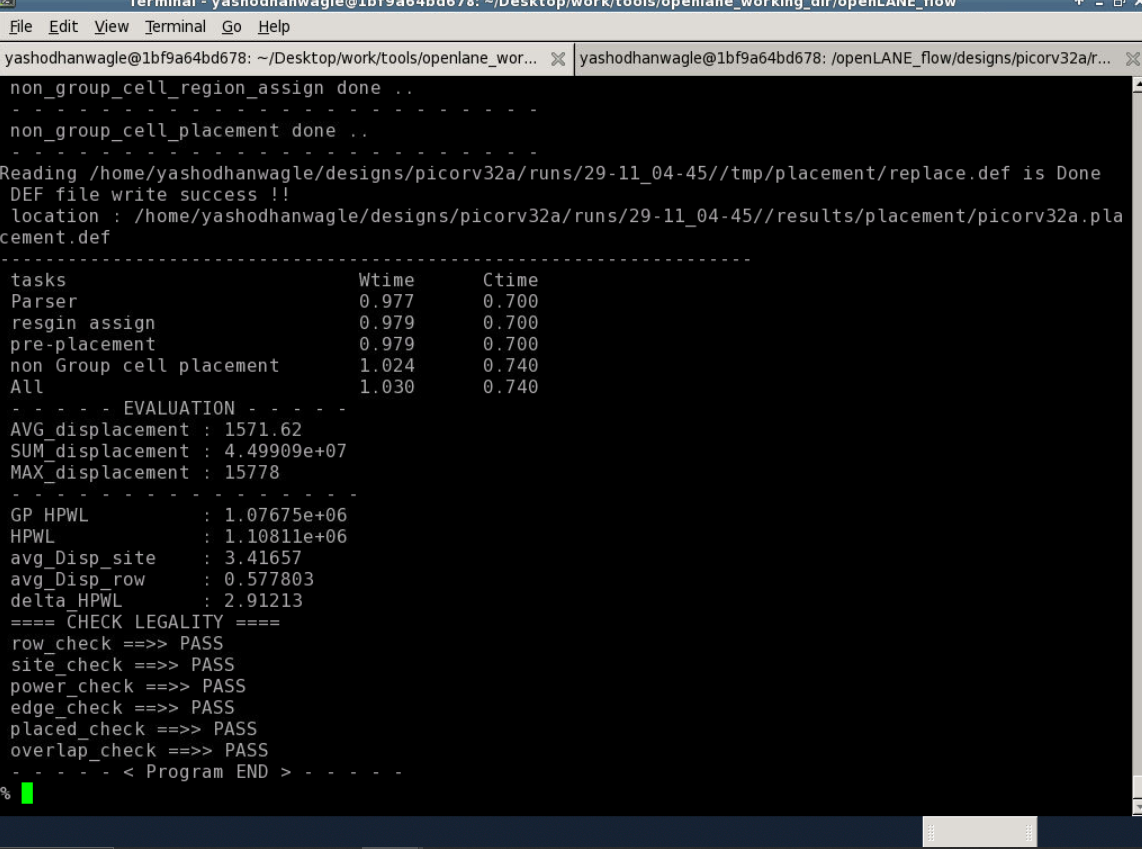

- Placement

- Standard cell design and characterization

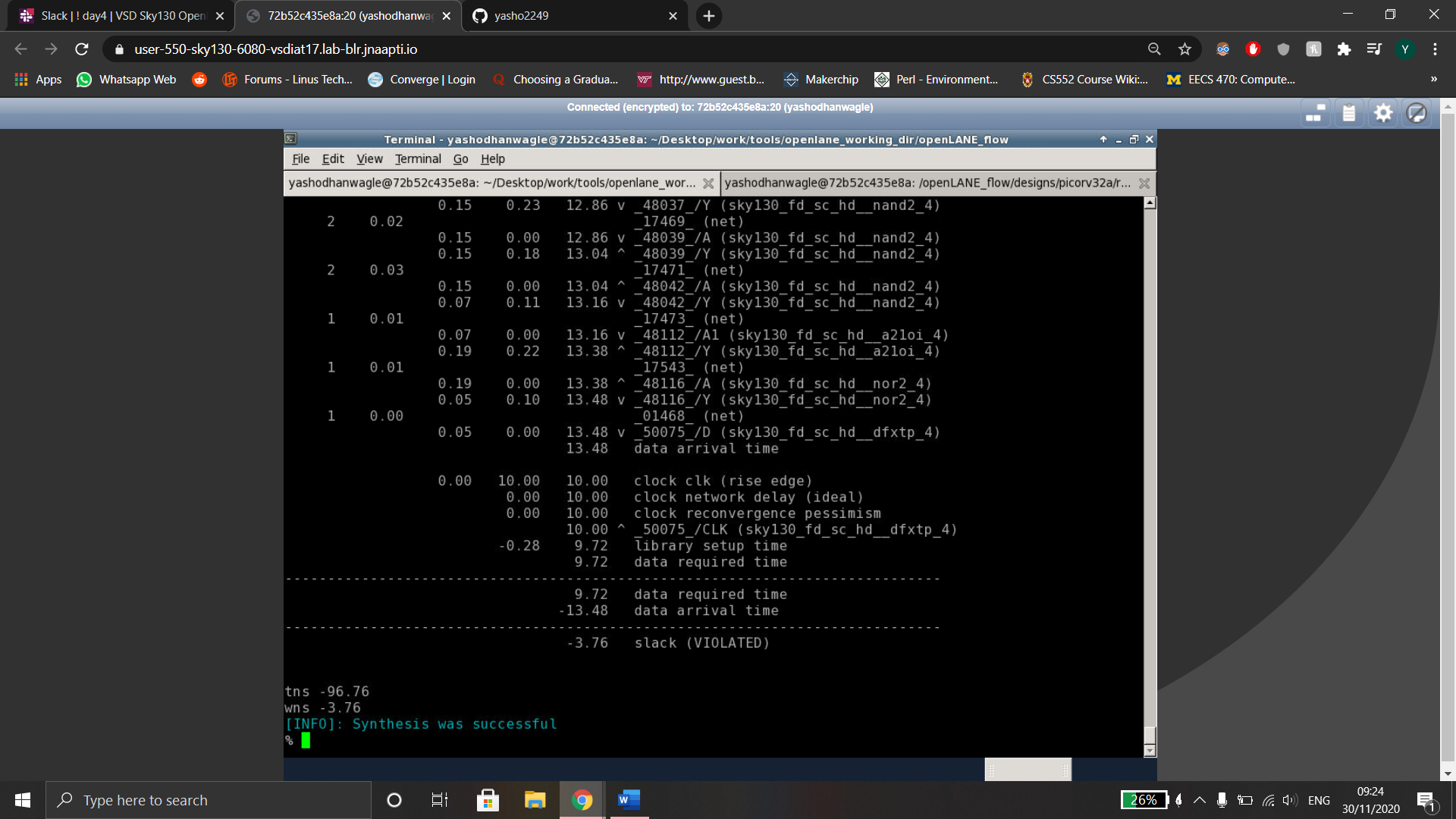

- Timing Analysis

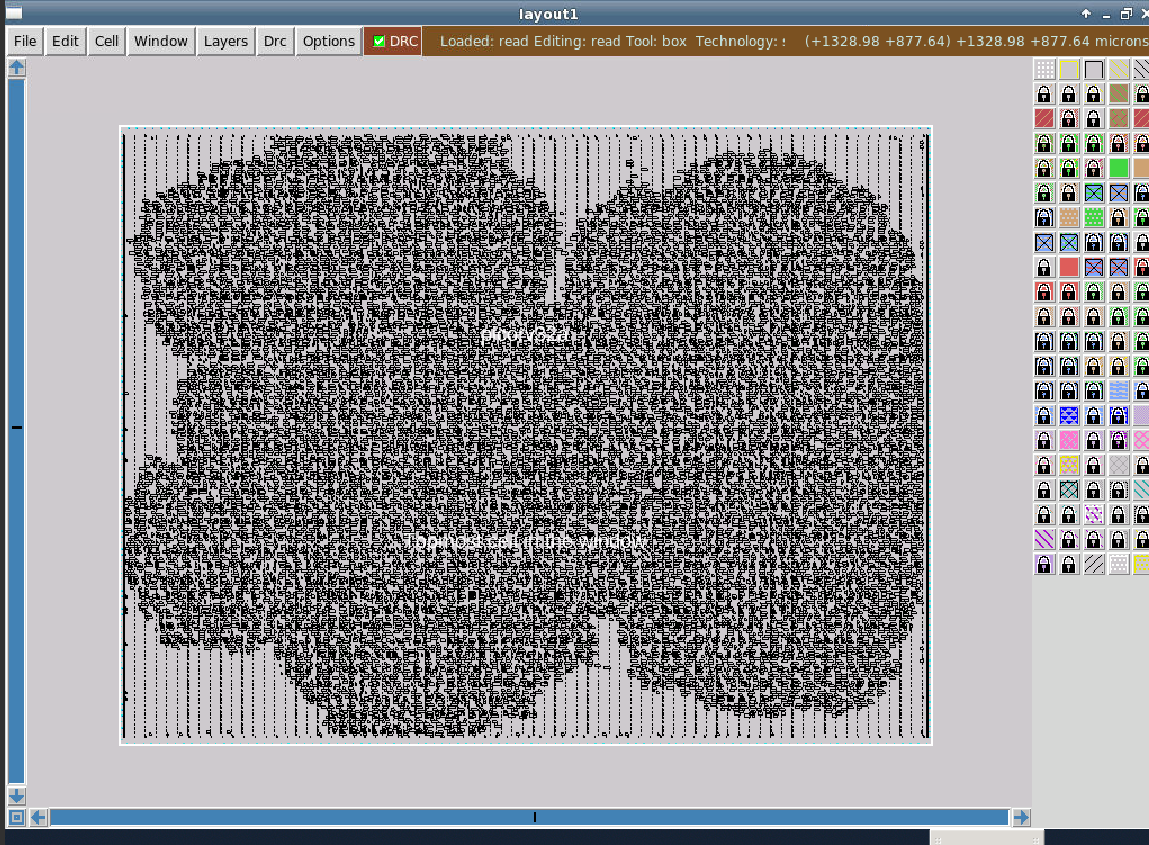

- Clock Tree Synthesis

- Routing

- DRC

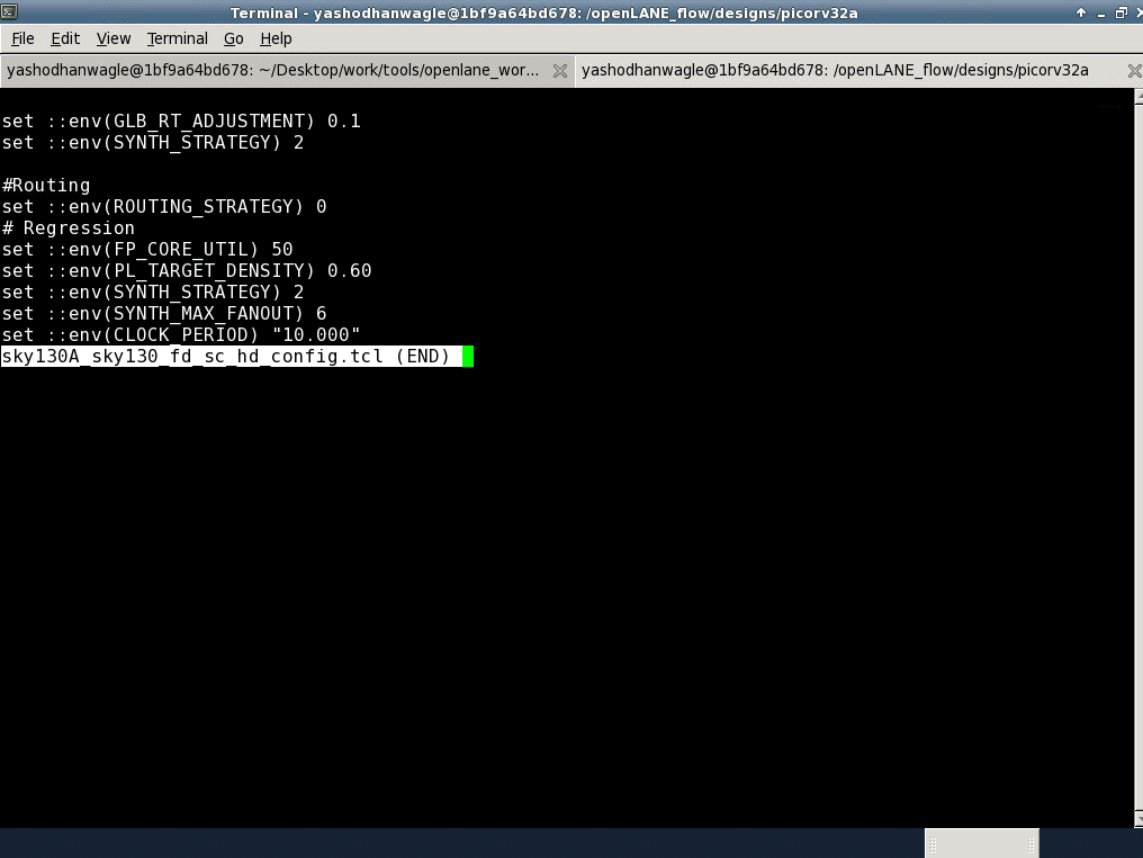

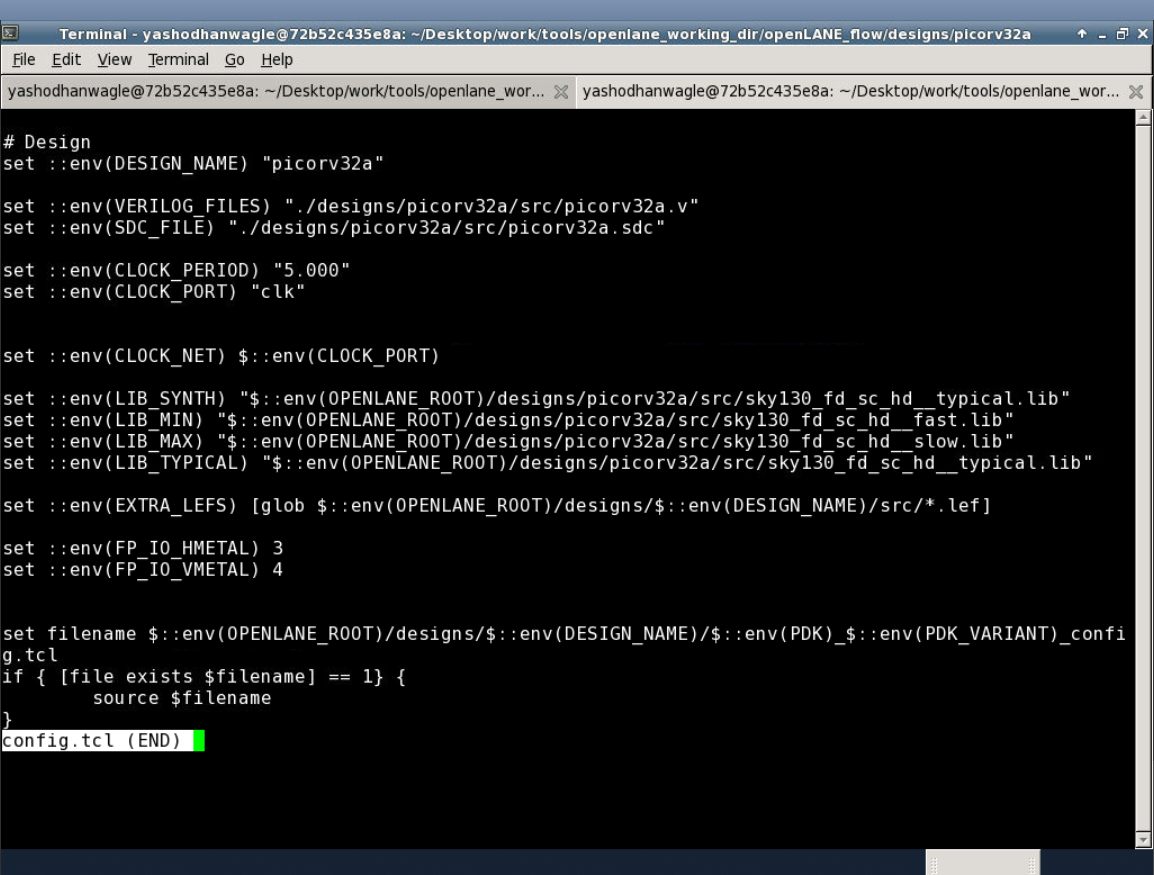

SkyLake130 config.tcl (highest priority):

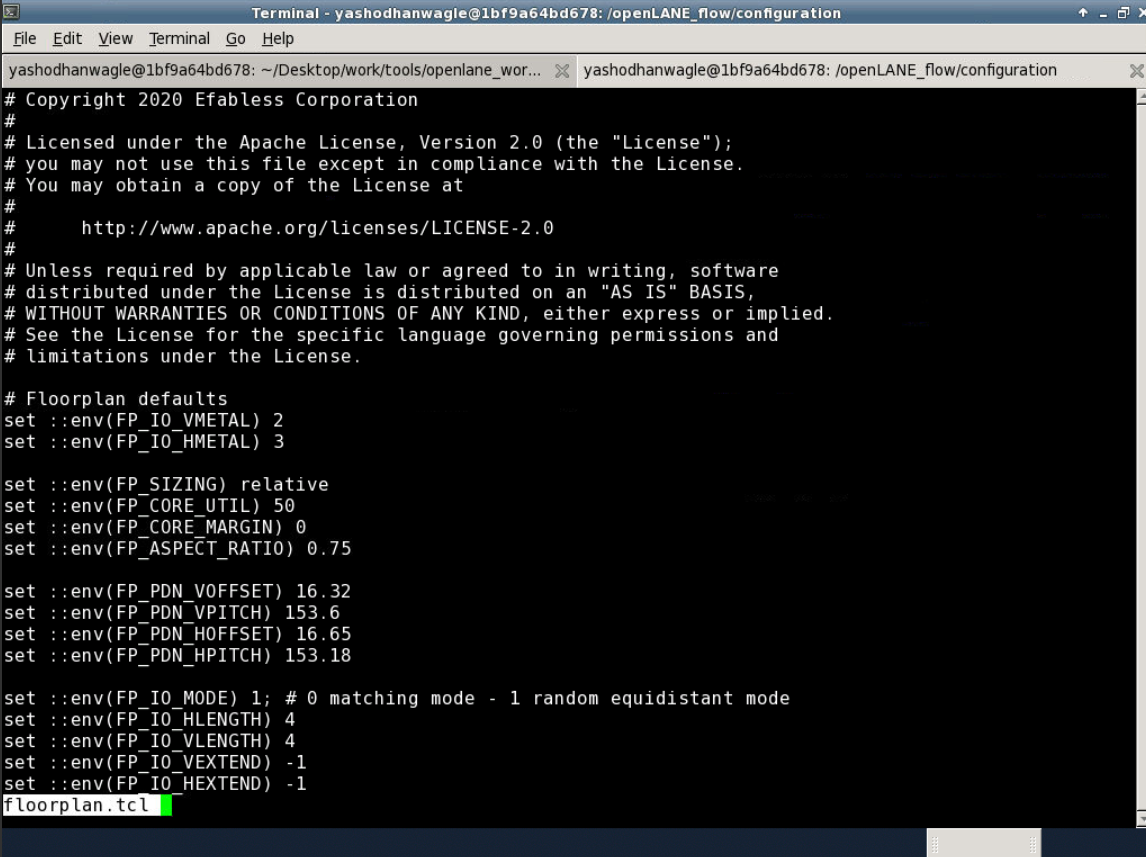

Floorplan Default config.tcl (lowest priority):

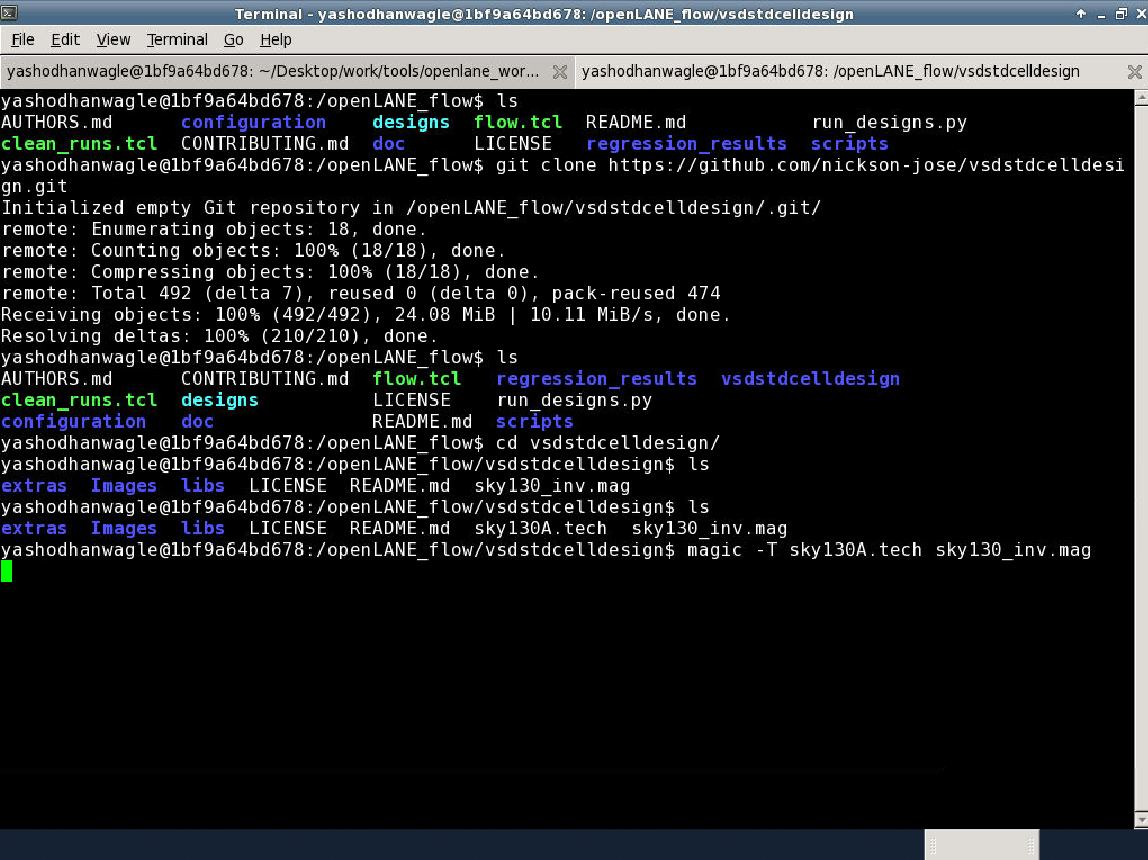

Cloning the required custom cell files:

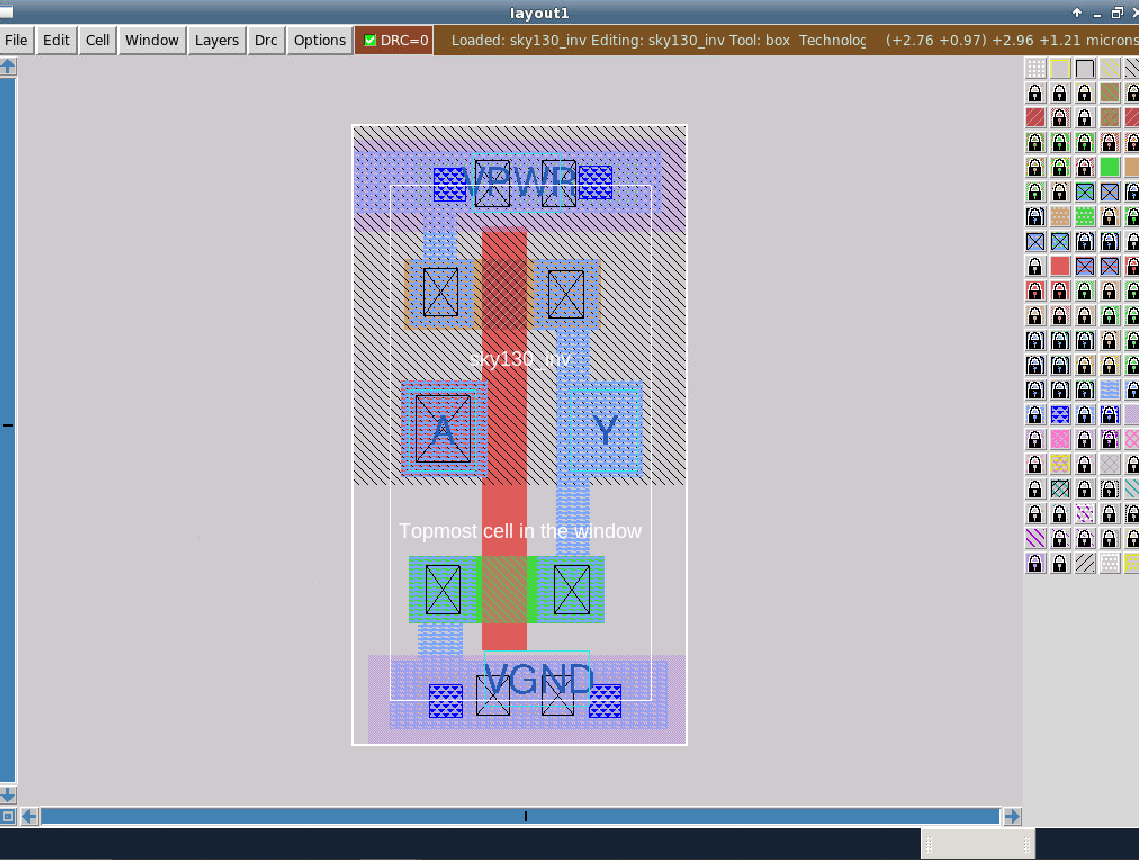

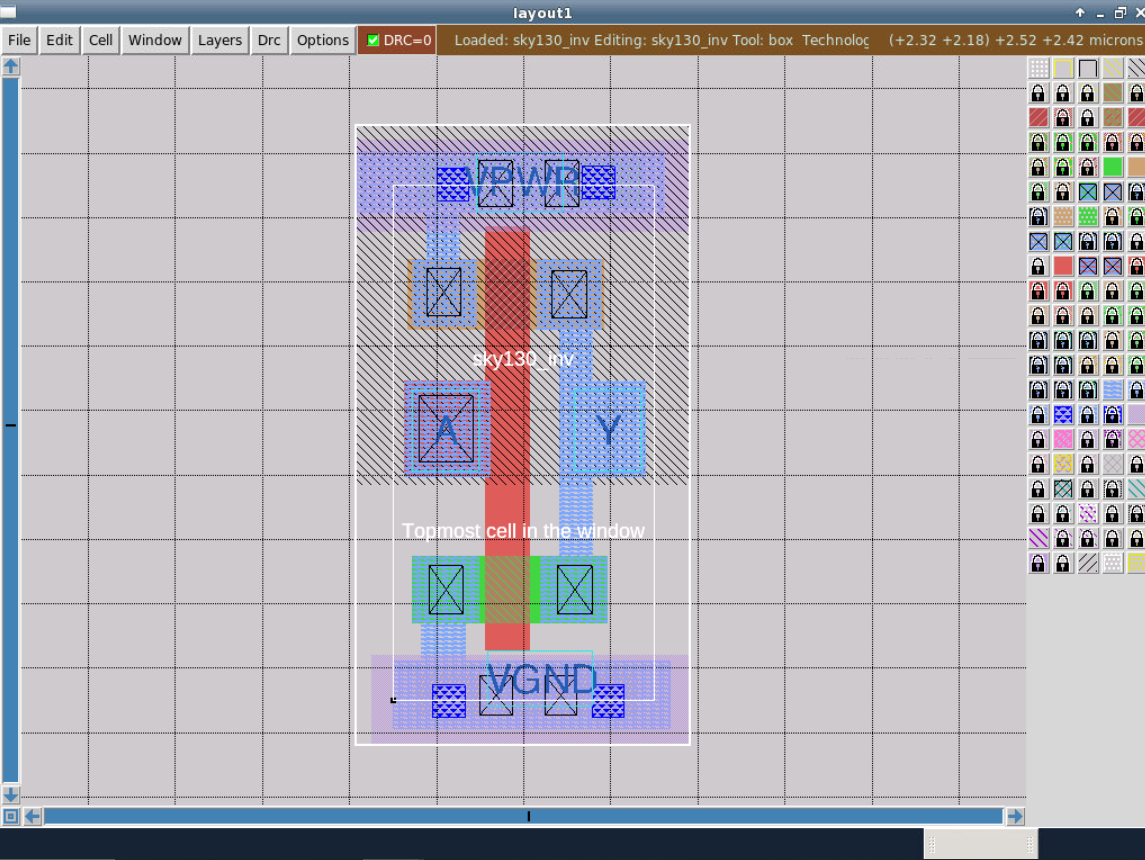

Custom Inverter Cell on Magic:

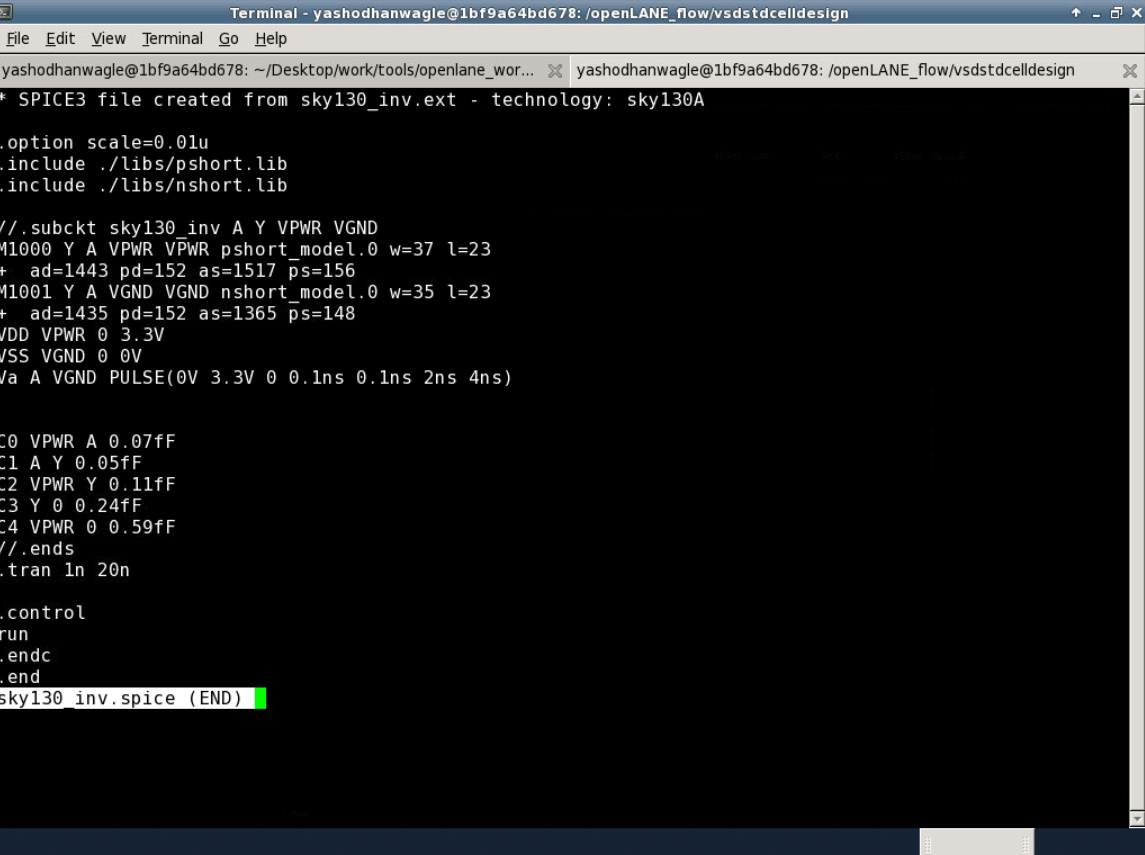

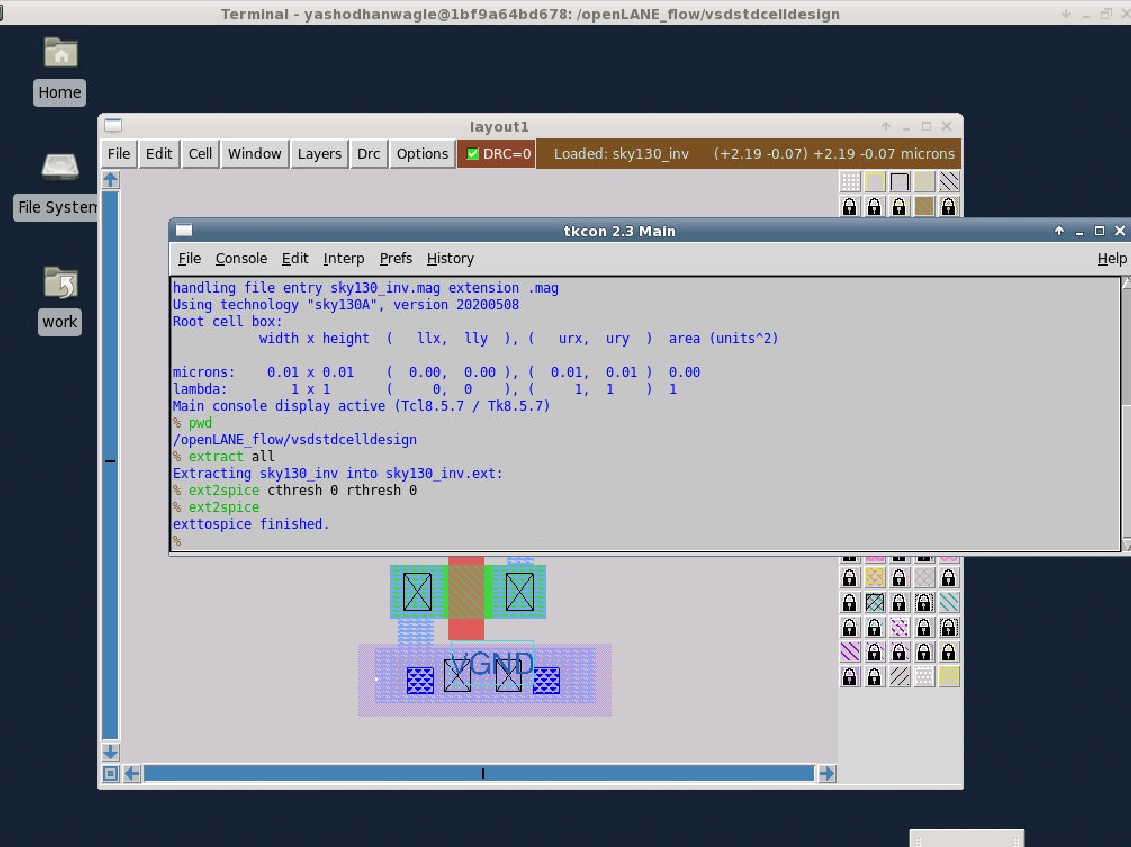

Export to Ngspice for analysis:

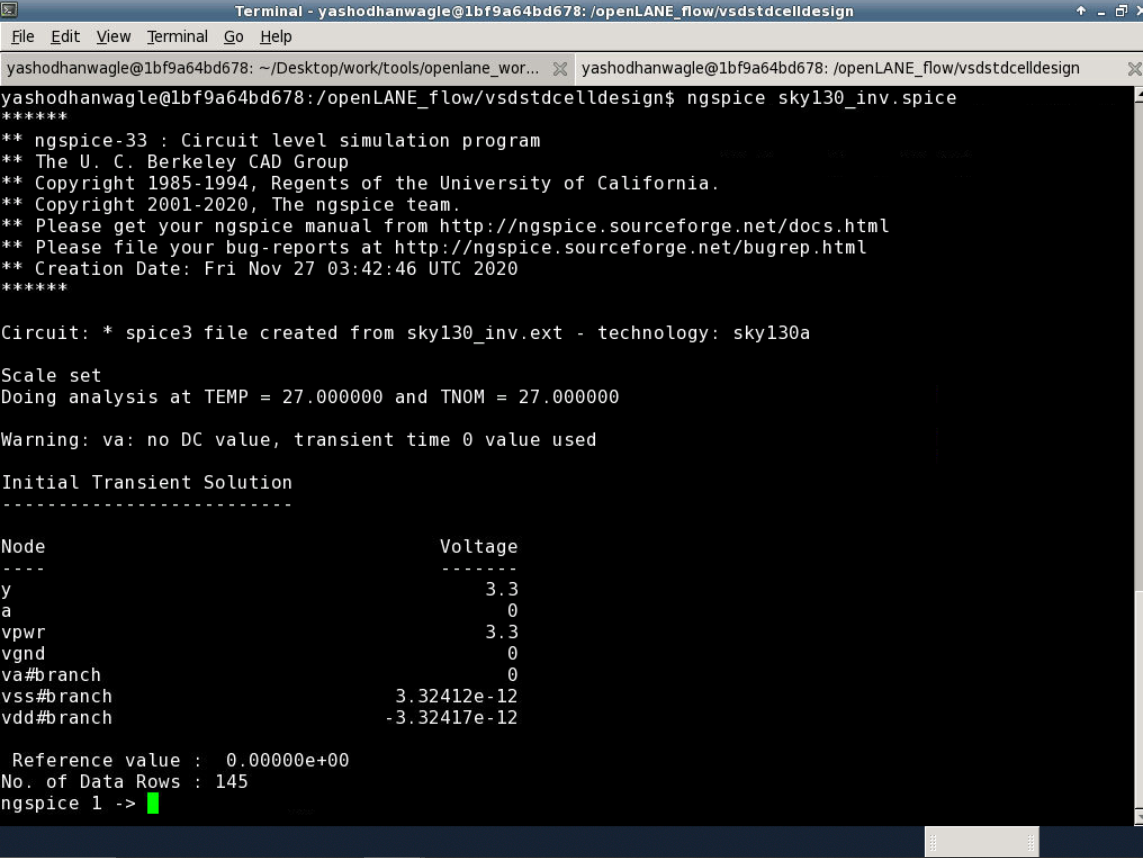

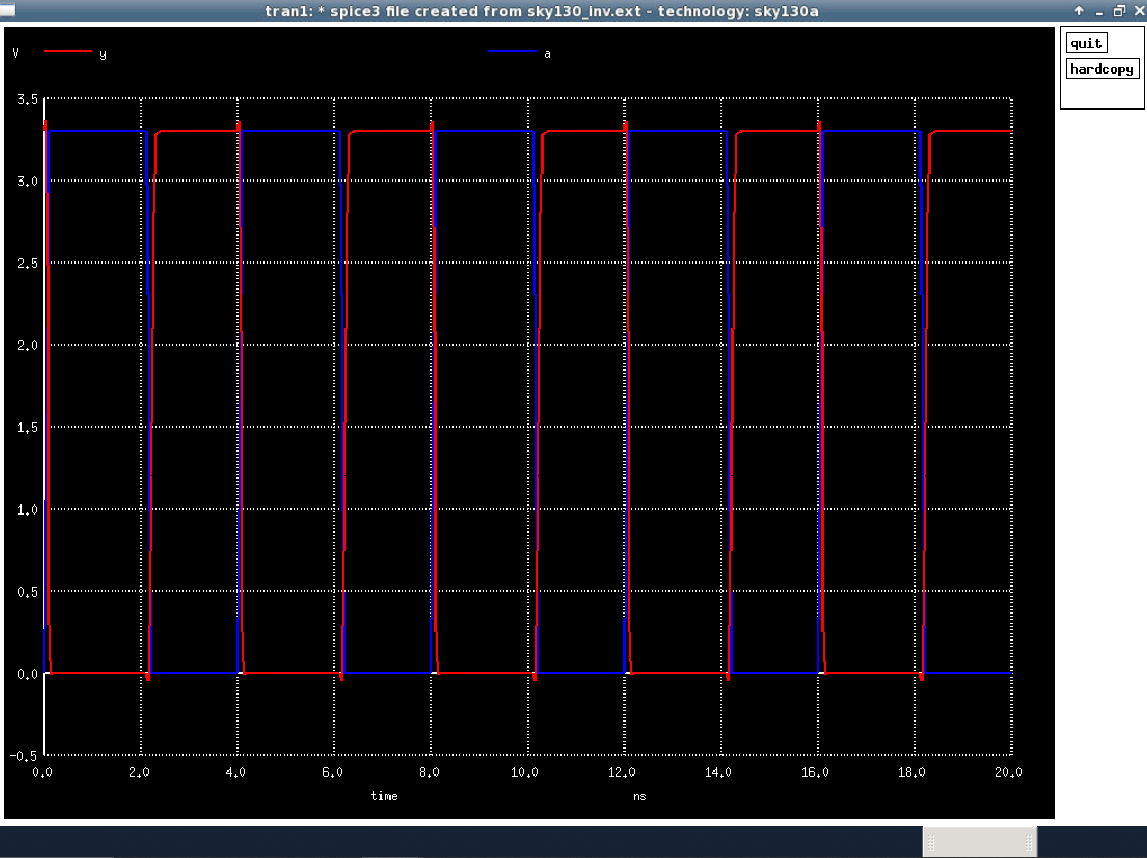

Transient Analysis of Custom Inverter Cell:

Lef file of Custom Inverter Cell:

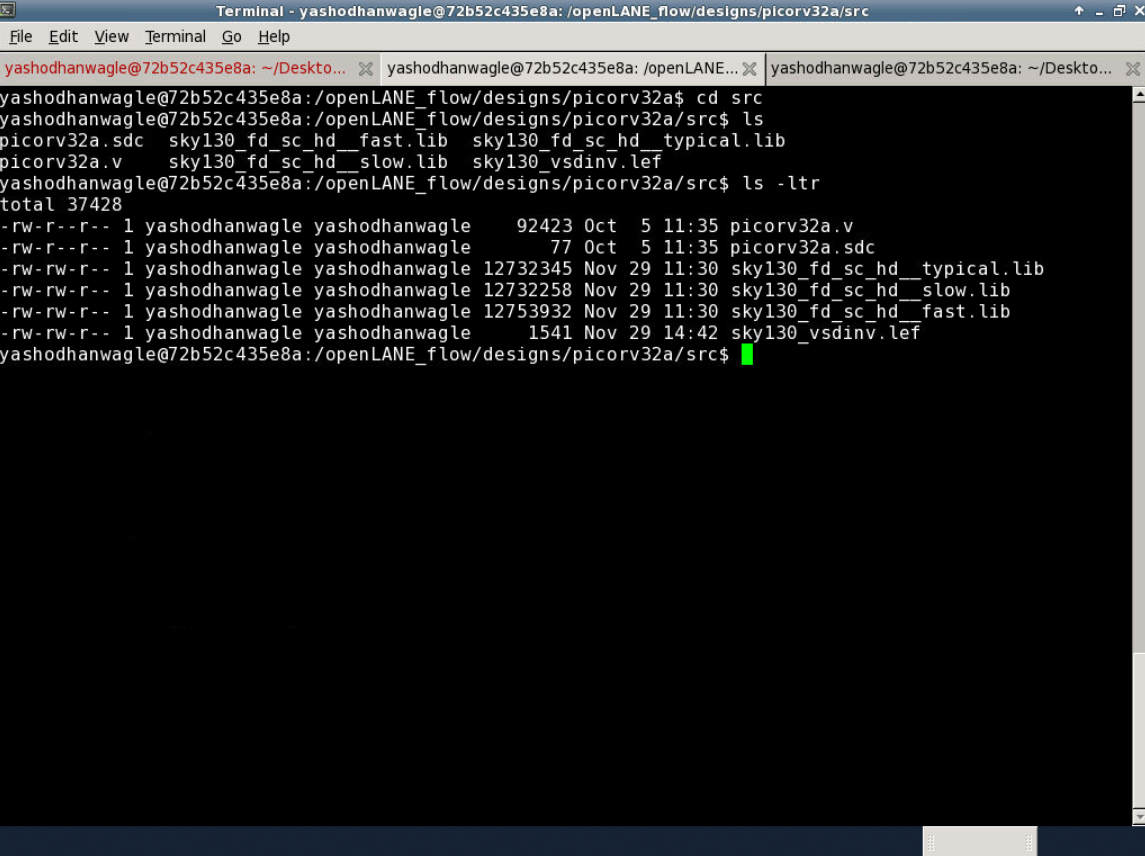

Lib file for inclusion of custom cell:

Custom config for inclusion of custom cell:

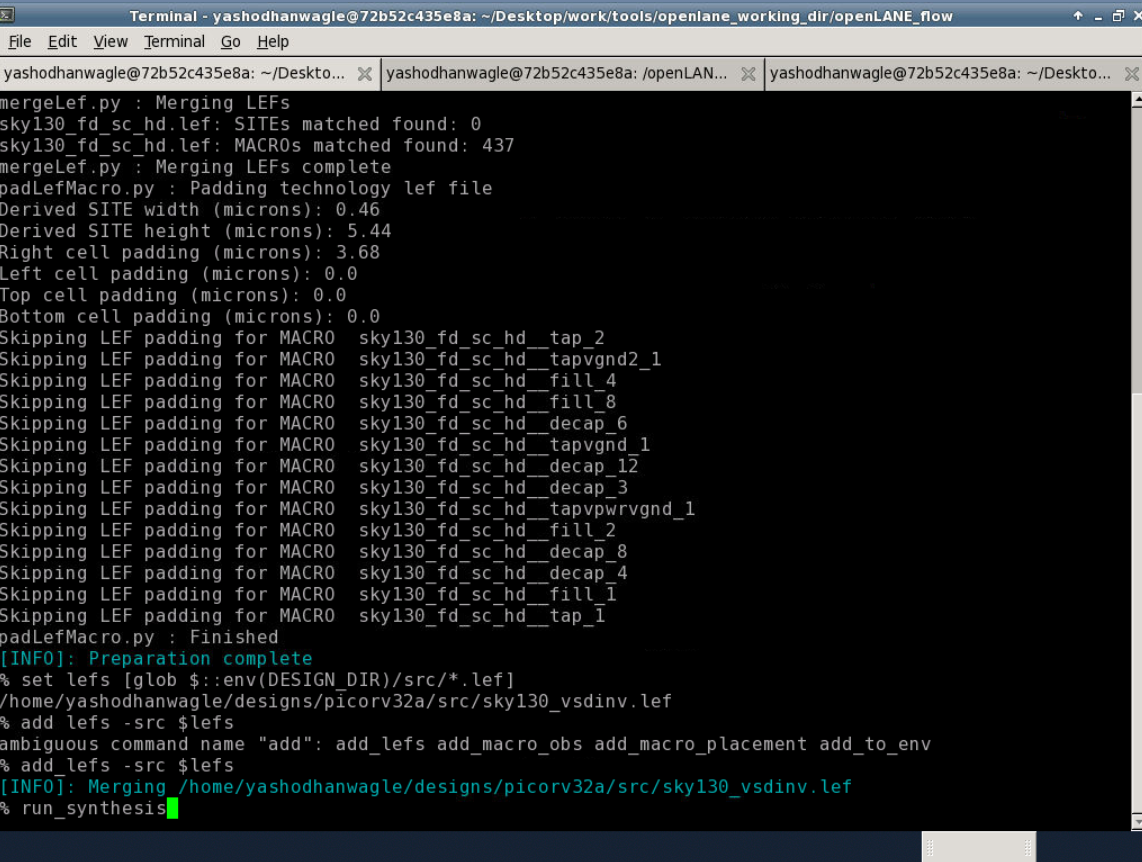

Synthesis prep witj custom inverter cell:

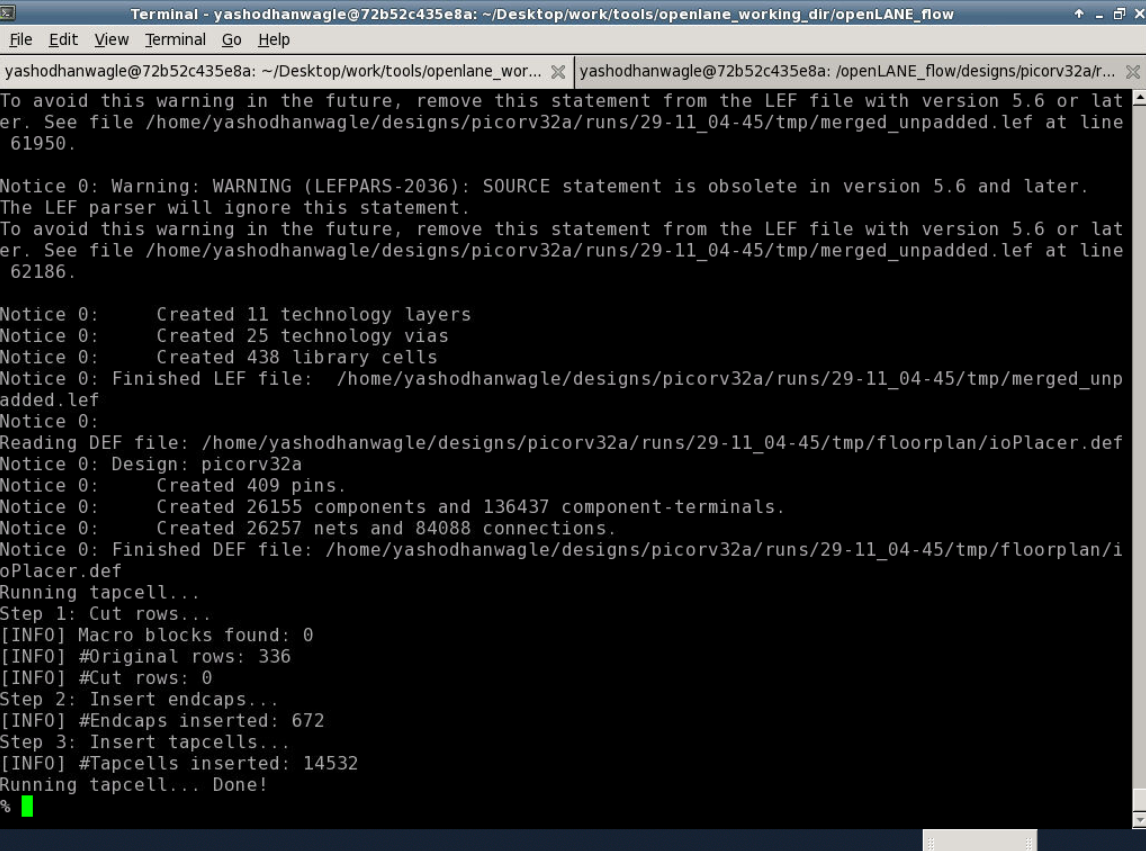

Floorplan with custom Inverter cell:

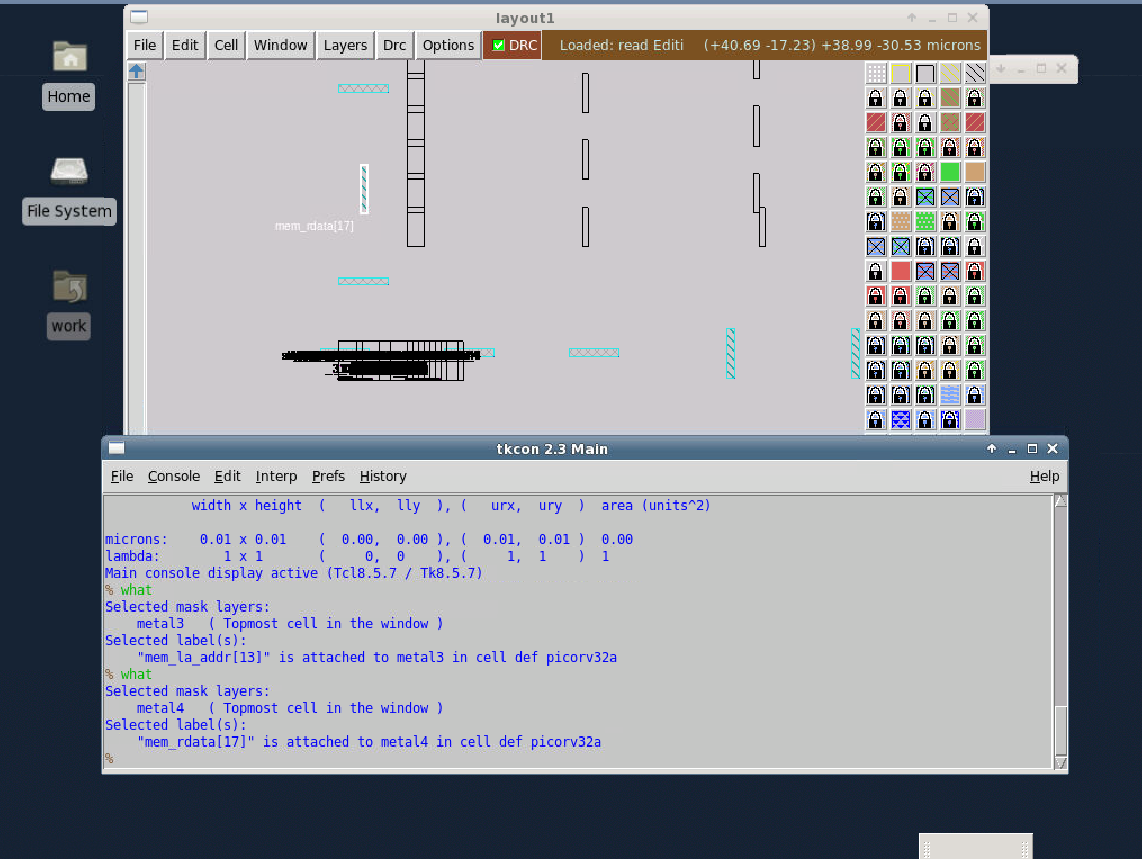

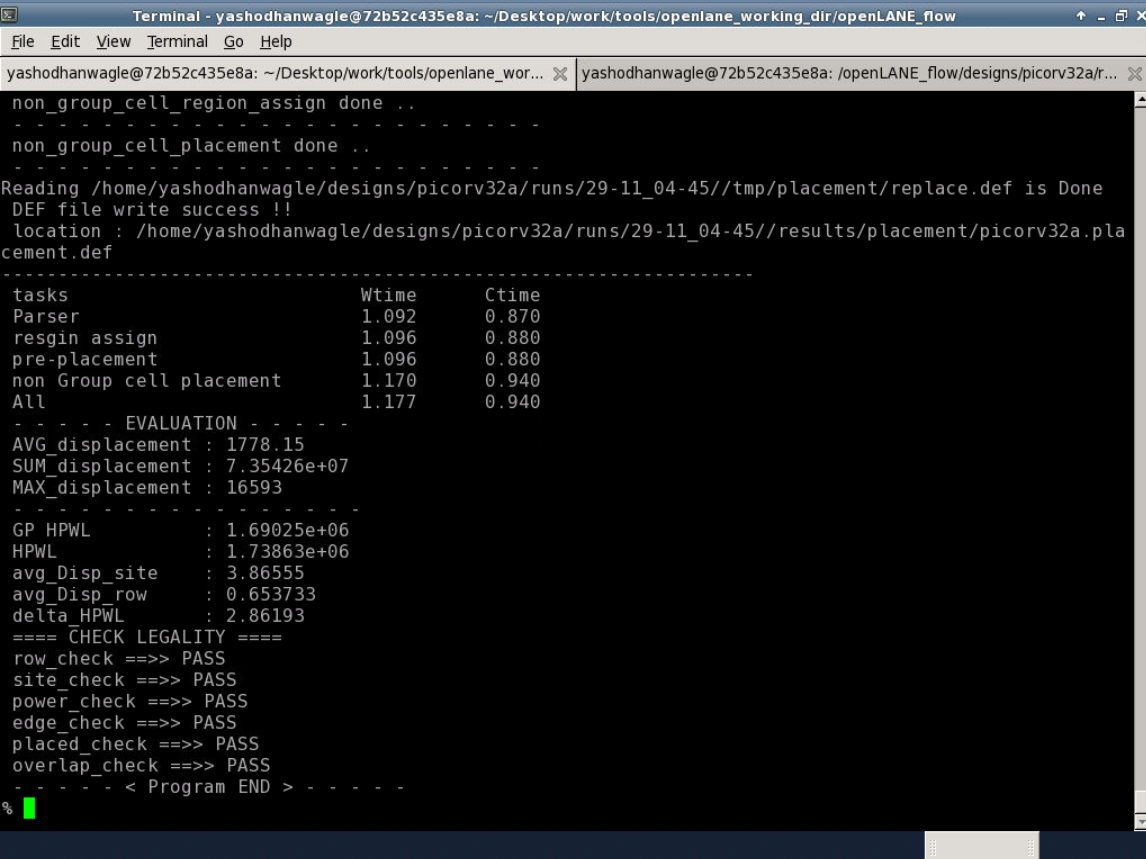

Placement with Custom Inverter celll:

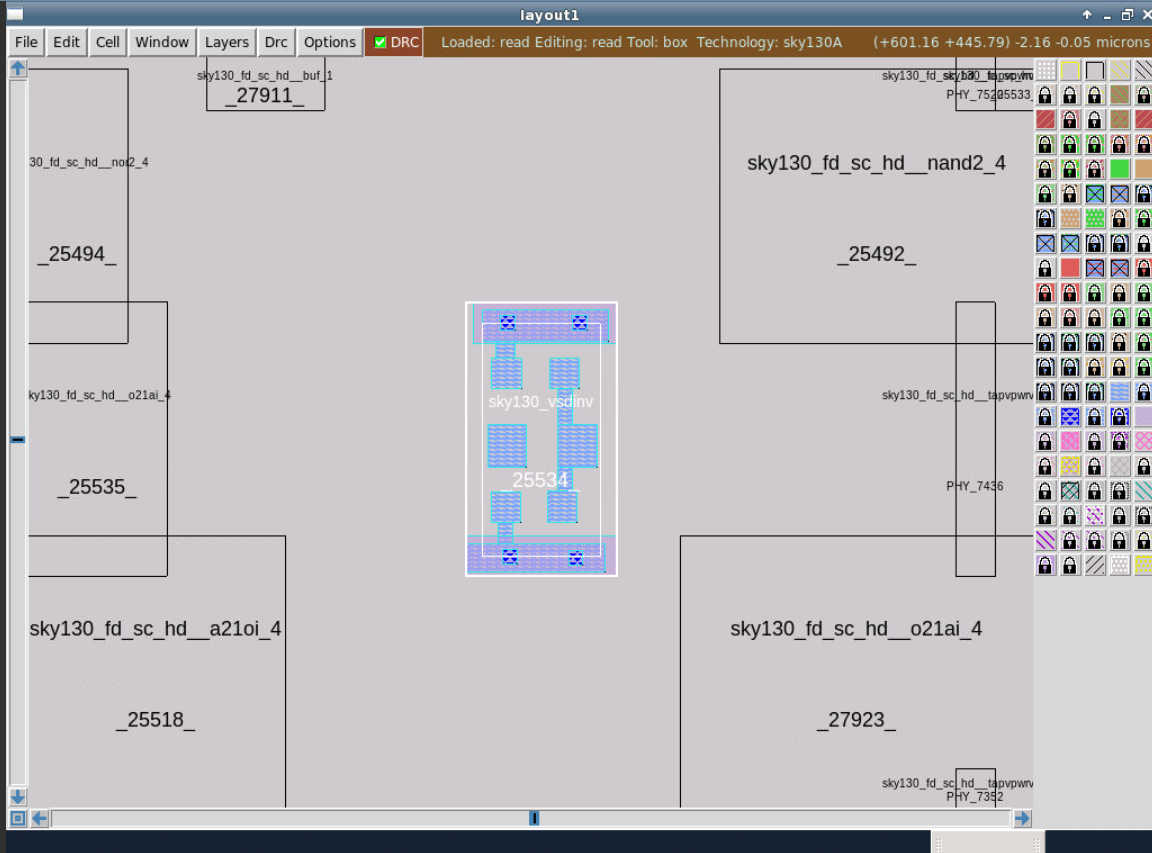

Placement of custom inverter cell on Magic:

Command for CTS. Ran with the default config.

run_cts

The output of CTS stage will provide a new netlist in ~/results/synthesis/ folder name picorv32a.synthesis_cts.v