Express open-DLA implementation kit for FPGA demo, revised based on NVDLA

- FPGA_RTL_nvsmall64 contains the source RTL codes that are revised for FPGA implementation.

- Prebuilt contains prebuilt and quantized DNN models (Resnet & Tiny YOLO) for standard application demos.

- nvsmall64_zcu104 contains the Vivado project for Xilinx MPSOC ZCU104 board.

- nvsmall64_zcu102 contains the Vivado project for Xilinx MPSOC ZCU102 board.

- ITRI (Industrial Technology Research Institute), founded since 1973, is Taiwan’s largest research institutions.

-

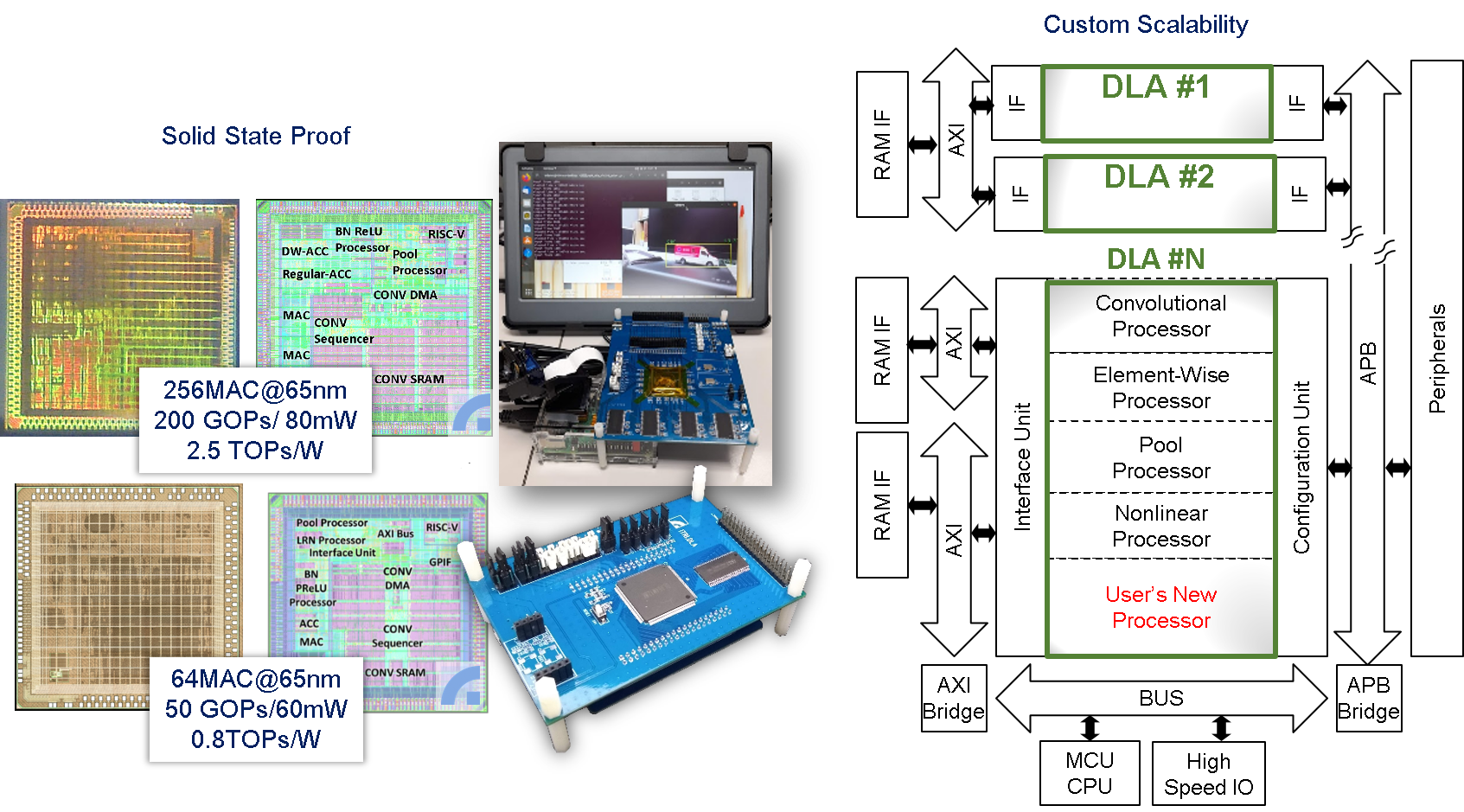

DLA (Deep Learning Accelerator), is a flexible DNN processing engine opened by NVDIA. We have revised this open source with several features, including the support of MobileNet Series, weight decompression of convolution / fully-connected operations, and various customize options for users. However, abovementioned revisions are under our commercial license, not inside this open project. This project is a basic revision that is close to the original open-source version.

-

About more information, please visit our public publications.

-

AI系統晶片解決方案,電腦與通訊2020

-

NVDLA軟硬體整合歷程 ,電腦與通訊2020

-

Customization of a Deep Learning Accelerator , VLSI-DAT 2019

-

Configurable Deep Learning Accelerator with Bitwise-accurate Training and Verification,VLSI-DAT 2022

-

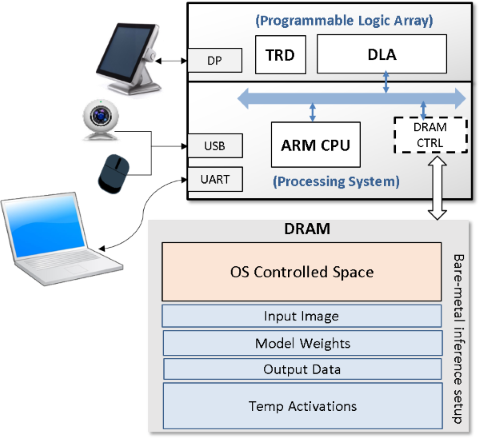

- The OpenDLA here is the basic one, 64-MAC version, which is originally named nv_small in NVDIA's open source. Here we provide the synthesizable codes and project files for popular Xilinx MPSOC FPGA Series. We hope this may create an easy entrance for DNN edge implementation whether in academic or industrial. Also, this can be a fast way to evaluate our services.

Contact me : scluo@itri.org.tw