SingleCycleCPU, as its name reveals, is a hardware program that simulate the behavior of a trivial single cycle CPU. As a homework assigned in the computer organization course for sophomore majoring in CS, it is an individual project for non-comercial purposes.

- Design the Datapath, bring together the basic units into Single-cycle clock CPU

- Implement at least 9instructions: Add, Sub, And, Or, Lw, Sw, Slt, Beq, J.

- Better implement the 16instructions: Add, Sub, And, Or, Addi, Ori, Sll, Srl, Lw, Sw, Slt, Beq, Bne, J, Jal, Jr

- Verify the CPU with program and observe the execution of program

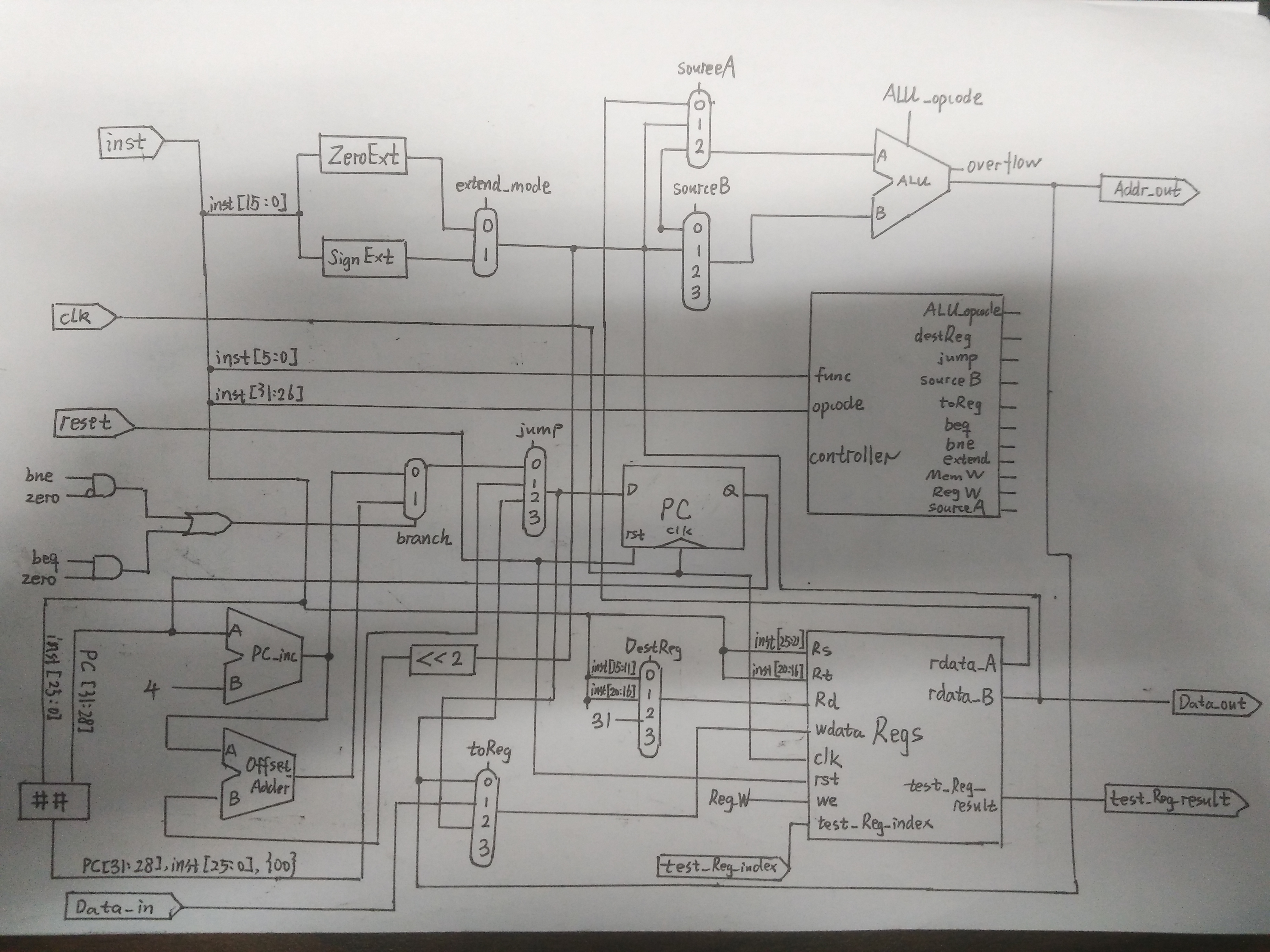

Here is the draft of my circuit implementing the CPU:

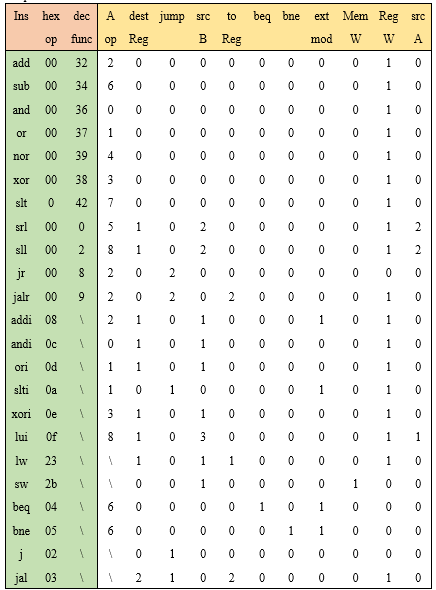

After construction the datapath well, we also need a signal truth table in order to implement controller.

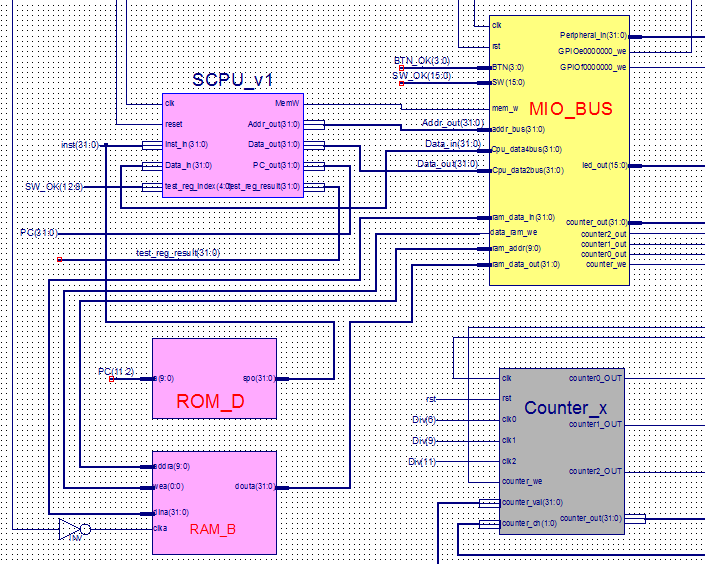

Now we can have a look at the interface of my SCPU, and the relationship between the SPCU and its neibours.

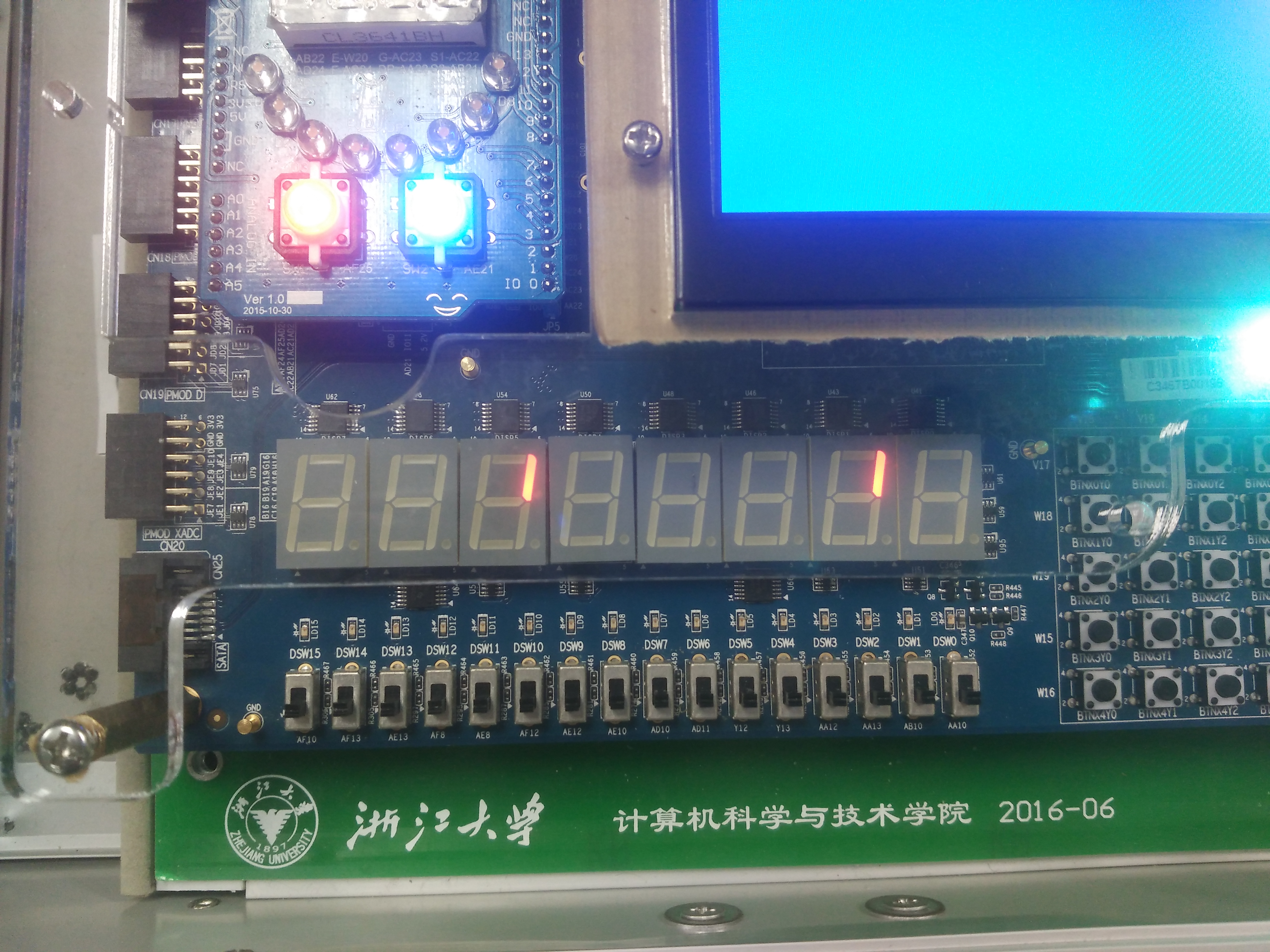

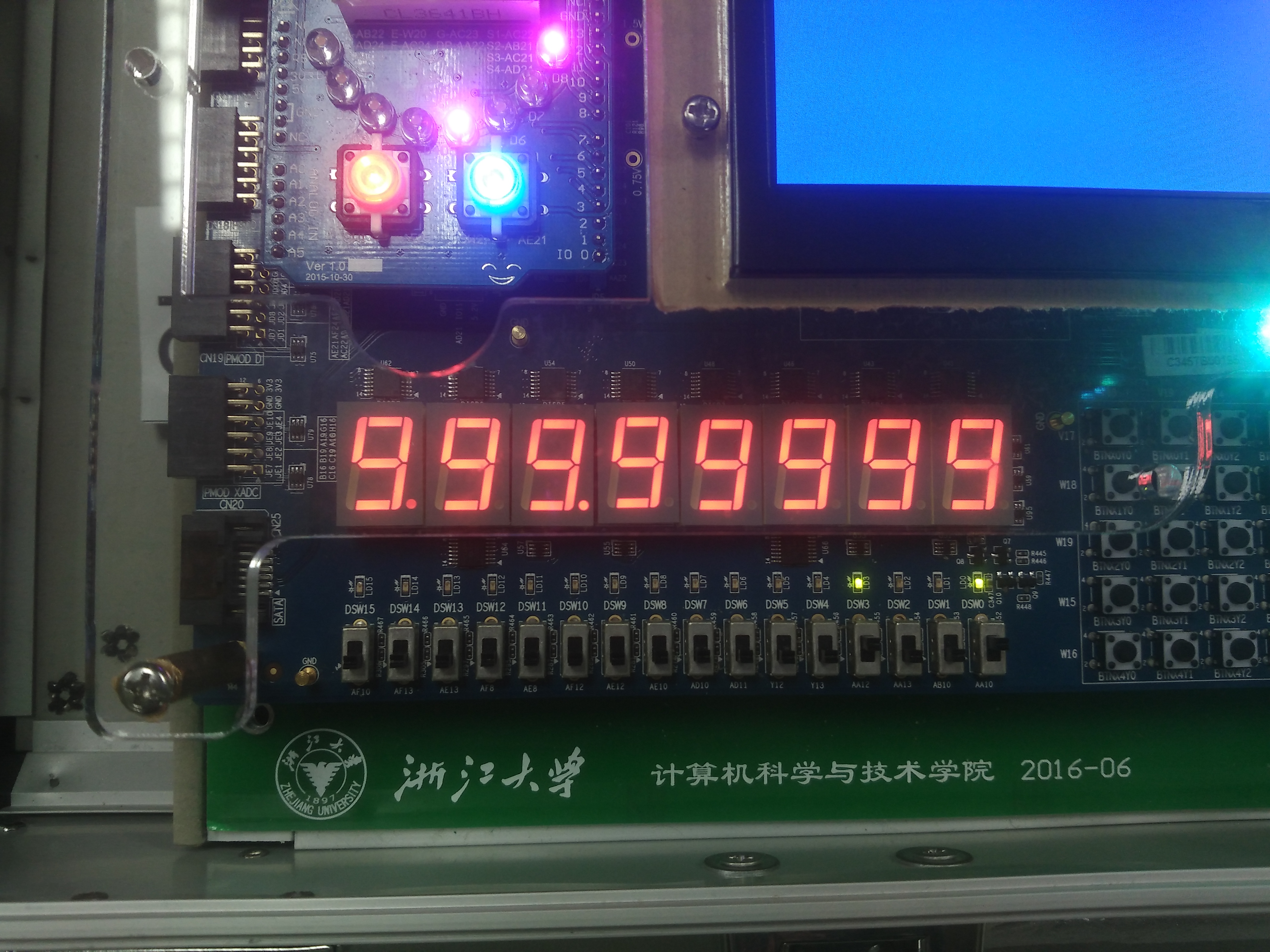

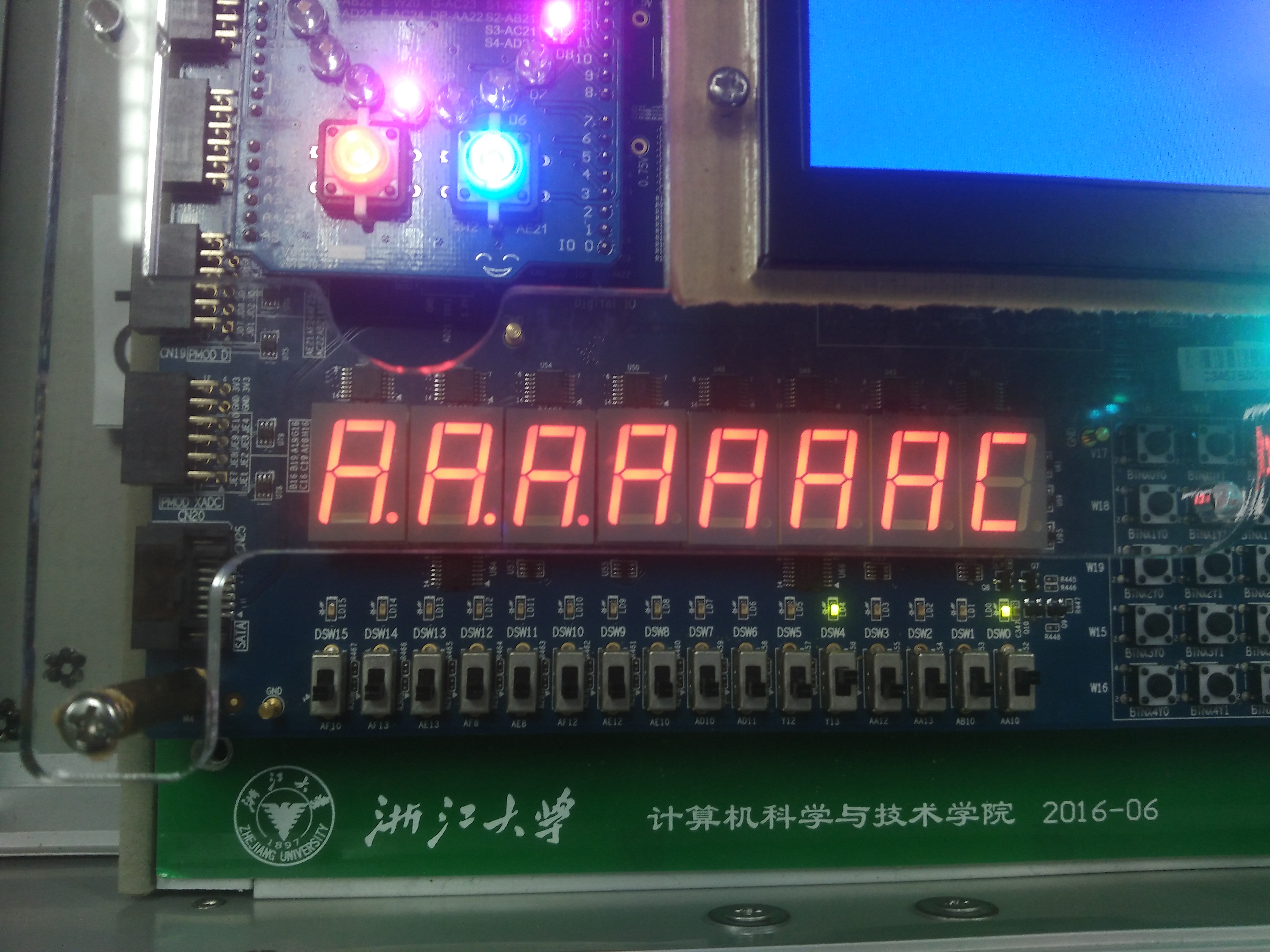

Everything went well in the following four tests:

The content of all the codes are supposed to use a licence AGPLv3

- Learn what is a AGPLv3, if you have not yet done so (see details above).

- Create your change to the repo in question.

- Fork the desired repo, develop and test your code changes.

- Ensure that your code is clear and comprehensible.

- Ensure that your code has an appropriate set of unit tests which all pass.

- Submit a pull request.

- The repo owner will review your request. If it is approved, the change will be merged. If it needs additional work, the repo owner will respond with useful comments.

First of all, I would like to extend my sincere gratitude to my supervisor, Xiaohong Jiang, for her instructive advice

and useful suggestions on my learning on couputer organization.

I am also deeply grateful of Zhe Pan, the TA's help in the completion and assessment of this project.

High tribute shall be paid to Licheng Guo, whose profound knowledge of CPU and Verilog HDL triggers my inspiration for this brilliant project.