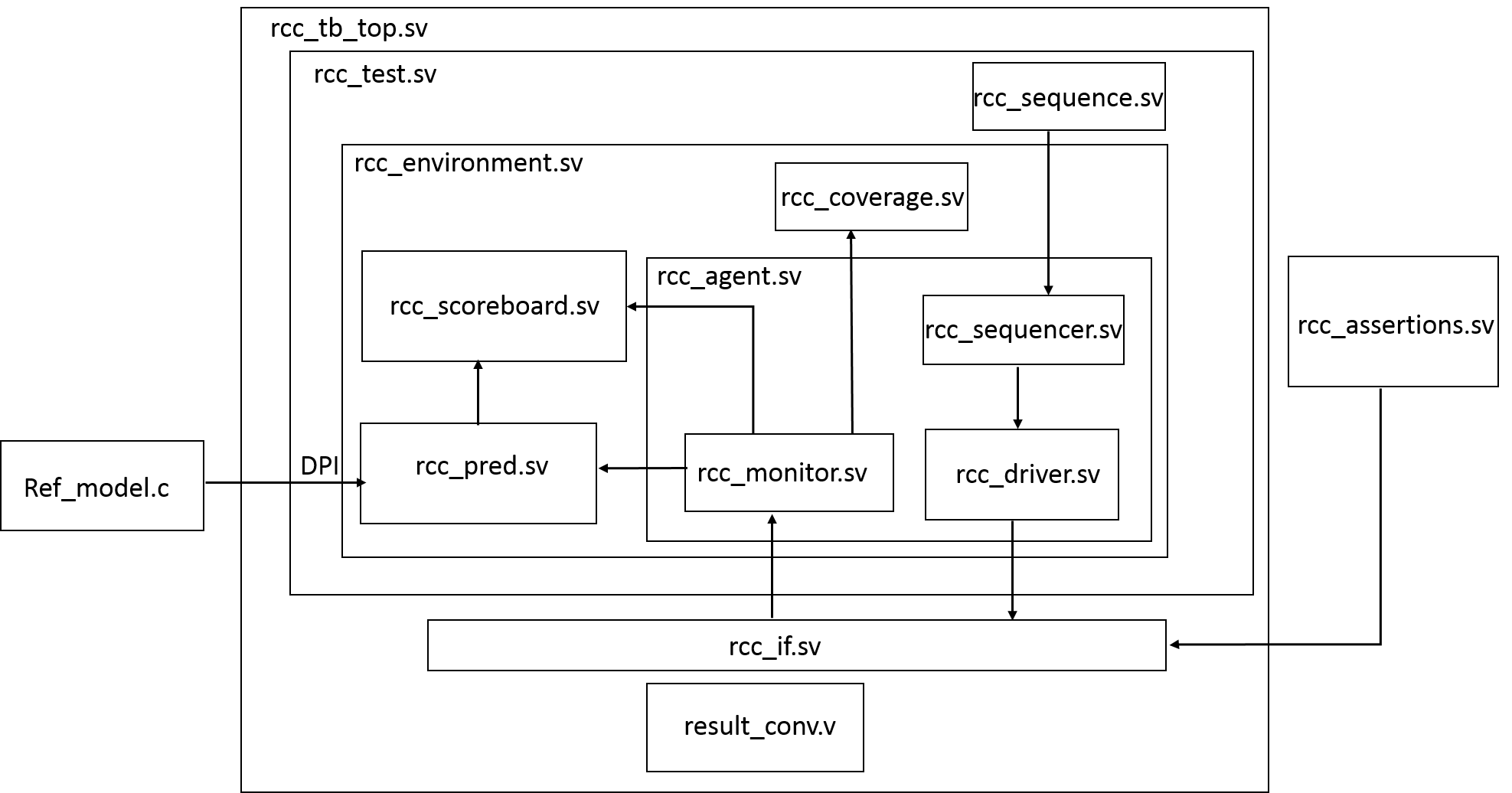

In this project a complete verification testbench architecture for a result character conversion chip is constructed.

- The testcase used for verification are the randomly generated input transactions for the DUT.

- Further the functional verification is performed by comparing the output of the DUT with that of reference model.

- To implement the reference model direct programming interface (DPI) functionality of SystemVerilog is used.

- The reference model is the software implementation of the DUT written using the C-programming language.