Typically, a Forth CPU has a core that functions as the Forth inner-interpreter with a small instruction set that represents the core primitive words. The Forth outer-interpreter is then built on top of these primitive words via cross-compilation on other development platform and copy onto the FPGA RAM either from external SD card or as binary image onboard ROM.

With the advance of SystemVerilog, having an outer-interpreter entirly in hardware is possible. Though the practicality of having it is in question, my task here is to give it a try to see how does and how well it work?

- This Google conversation sort of sealing the fate of this project. And, the answer is NOT REALLY!

- So, with spare time, I look at eJsv32 which was the extension of Dr. Ting's last project before his passing. (https://github.com/chochain/eJsv32/)

-

Serve as a temp storage before transition to the team project (https://github.com/angelus9/AI-Robotics/)

-

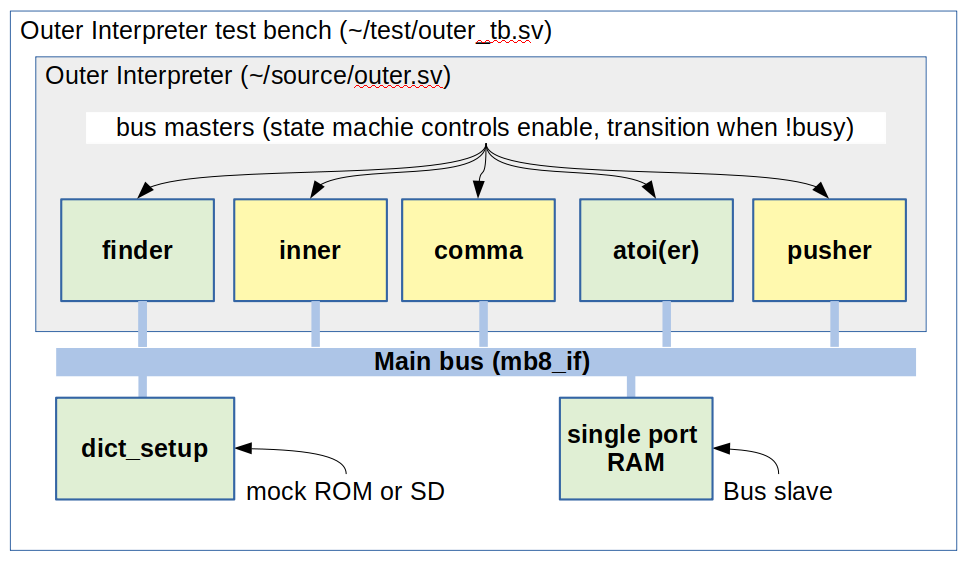

Functional units

Unit Desc Status Note Outer Top Module OK Atoi(er) ASCII to integer converter OK Finder Dictionary walker OK Comma Byte Compiler Mock Pusher Stack operation Mock Mem SPRAM dictionary pool OK 8-bit Exec Execution Unit OK 25 opcodes only Inner Inner-interpreter Mock Dict_setup Dictionary/TIB initializer OK

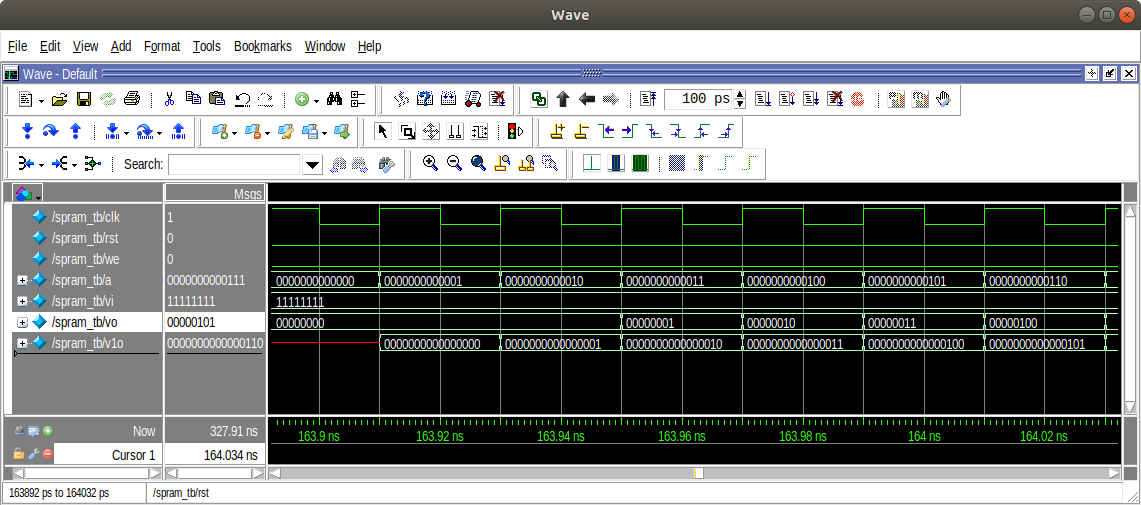

- Mem pool and Find

mem pool (single port RAM) find (dictionary search)

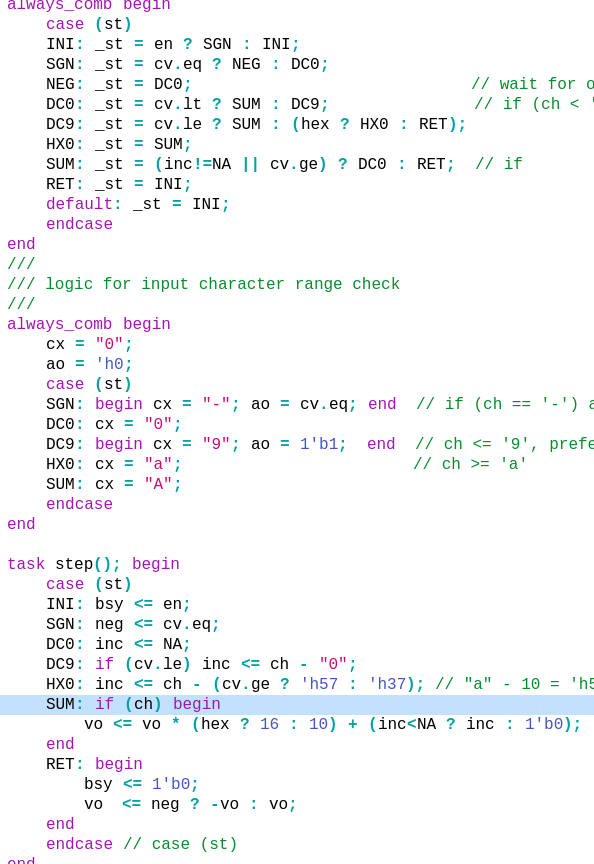

- Atoi (string to integer)

case0 case1 8-state, dedicated comparator 3-state, synthesizer gen comparators LUT 220 LUTS 182 LUTS src

syn

sim

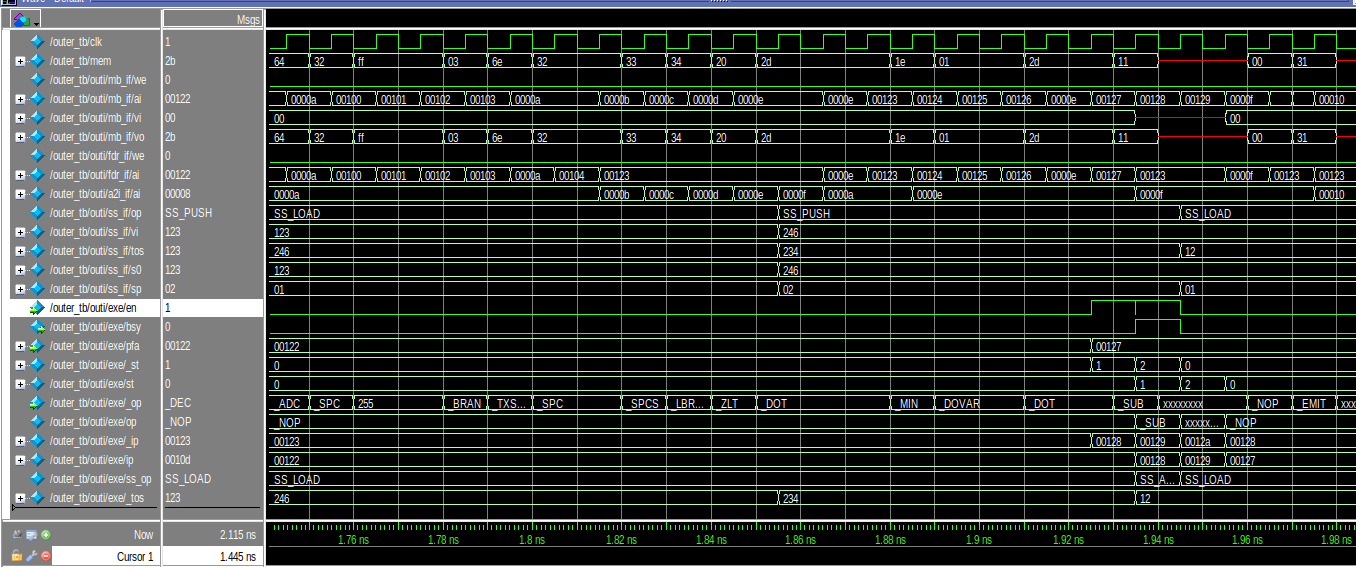

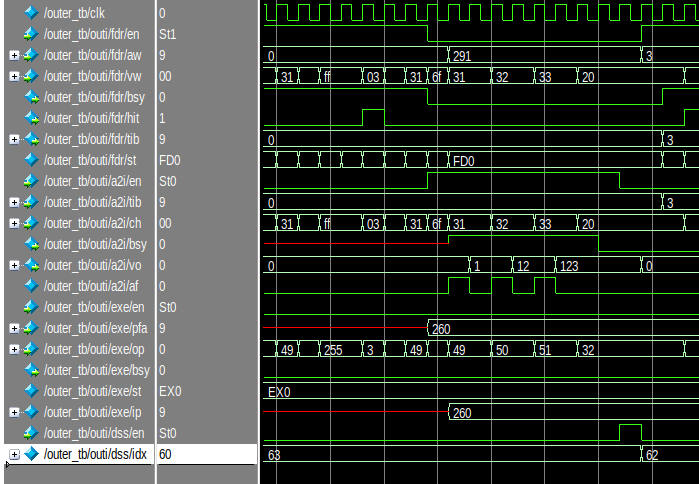

- Module transition (outer interpreter)

fnd -> a2i -> psh fnd -> exe -> fnd

- Execution unit

stack op ALU op

- Inner interpreter

123 dup + 234 -