uvm_tb_cross_bar is my a SystemVerilog UVM example.

It has DUT, testbench and scripts to run simulation.

A cross_bar project is used as DUT, this is just a bus switcher(specification).

Used my implementation of this design.

DUT implementation is located in the rtl directory.

For RTL synthesis is used Intel Quartus Prime, example is located in the quartus directory.

The testbench has bus and cross-bar UVC.

Bus UVC has agent and sequences packages.

Cross-bar UVC has agent, layer and virtual_sequences packages. The layer provides connectivity cross-bar and bus UVC.

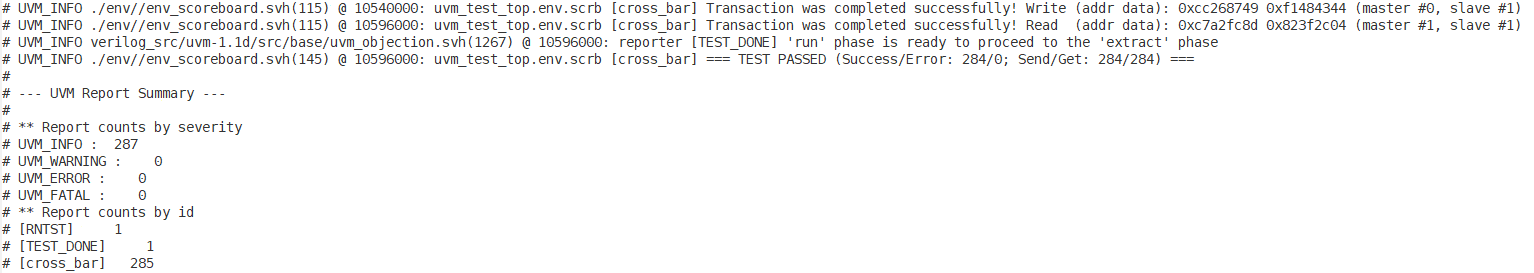

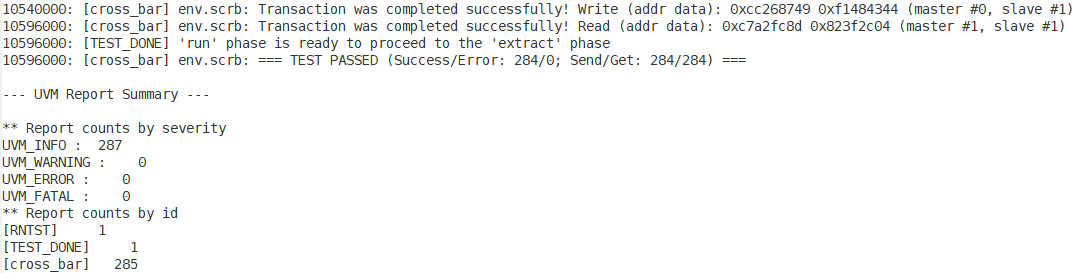

Env connected DUT, UVC and scoreboard. The scoreboard is checking results of each tests.

SystemVerilog UVM tesbench is located in the uvm_tb directory.

To run simulation of this example used Mentor Graphic’s QuestaSim or ModelSim simulator.

Directory sim contains files to run simulation.

Following examples of commands to be run from the sim directory.

To run the simulation used console and make-file.

To get list of available commands or list of tests should run following command from console:

$ make helpRun command from console:

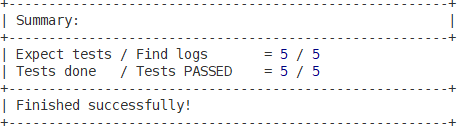

$ make all_testsThe results of each test and a summary of all the tests are displayed in the console.

Each test writes a log and report files: <test_name>.log, <test_name>.log.rpt (report file - it is just reformatted the log file).

At this example there are following ways to run tests:

- run test in console(without GUI)

- run test with GUI from console

- run test from GUI

To run test just run command from console:

$ make <test_name><test_name> - name from list of tests

Should set empty environment variable VSIM_MODE, and run test in console (example for BASH):

$ export VSIM_MODE=''

$ make <test_name>or

$ make <test_name> VSIM_MODE=''<test_name> - name from list of tests

Run ModelSim/QuestaSim, load aliases, run test.

- Run ModelSim/QuestaSim in

simdirectory

$ vsim `pwd` &- run in ModelSim/QuestaSim Transcript window

do alias.do- run test

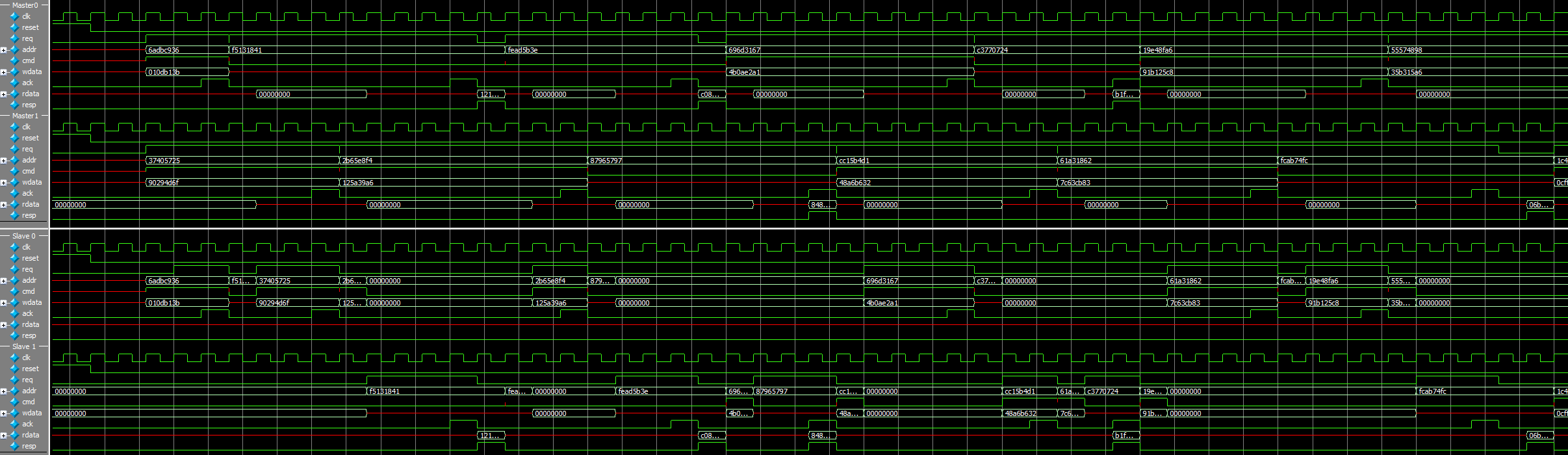

run_<test_name>Mentor Graphic’s QuestaSim wave

This project is licensed under the MIT License. If not, see https://www.opensource.org/licenses/MIT