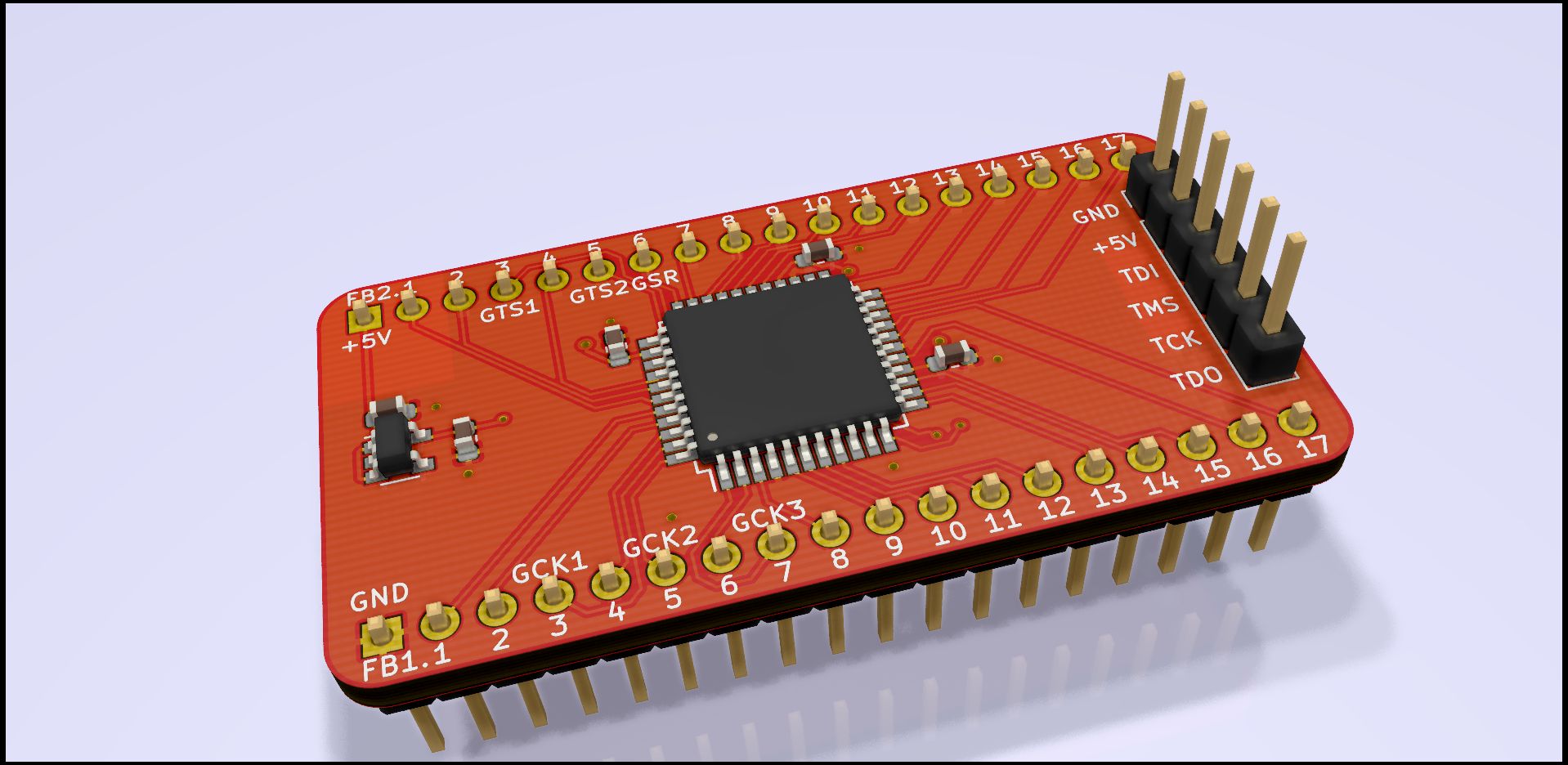

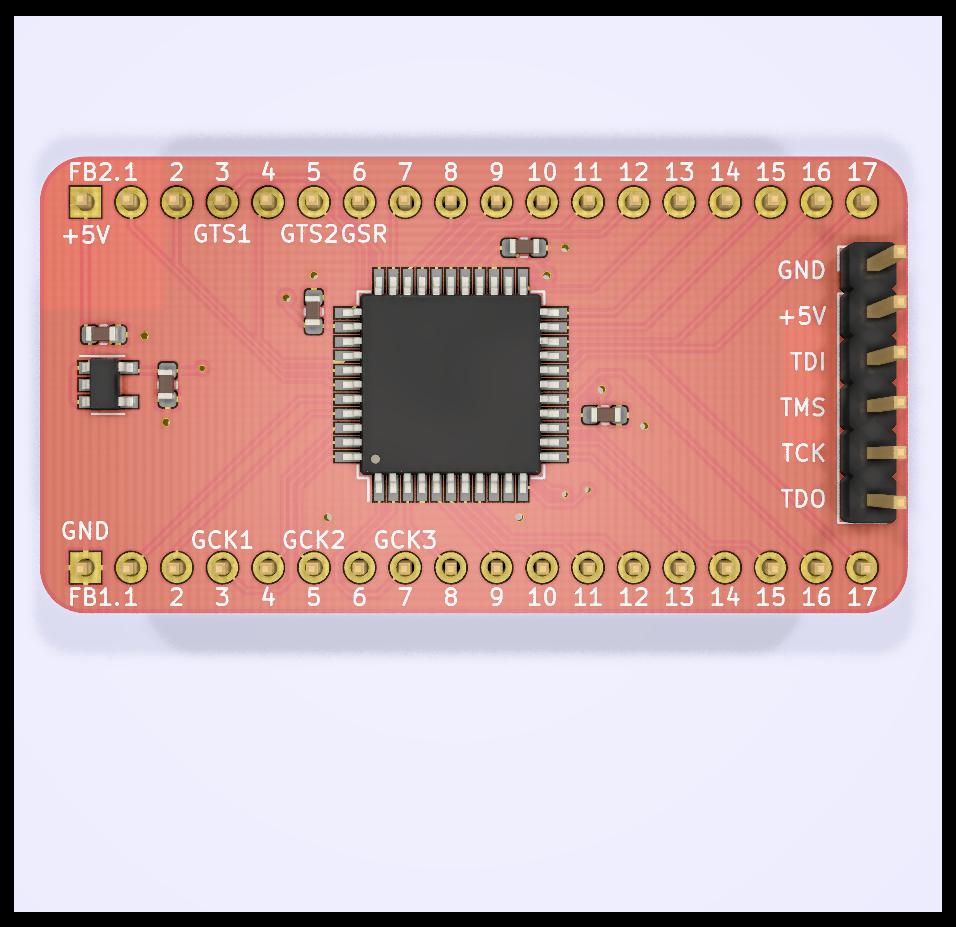

Rev A October 2019

- 5 ns pin-to-pin logic delays

- System frequency up to 178 MHz

- 36 macrocells with 800 usable gates

- 5V tolerant I/O pins (accept 5 V, 3.3V, and 2.5V signals)

- 3.3V or 2.5V output capability

- JTAG Programming Header

- 5V->3.3V Voltage Regulator to power XC9536XL

- XC9536XL is 5V tolerant and, with a 3.3V output, is compatible with in 5V TTL projects.

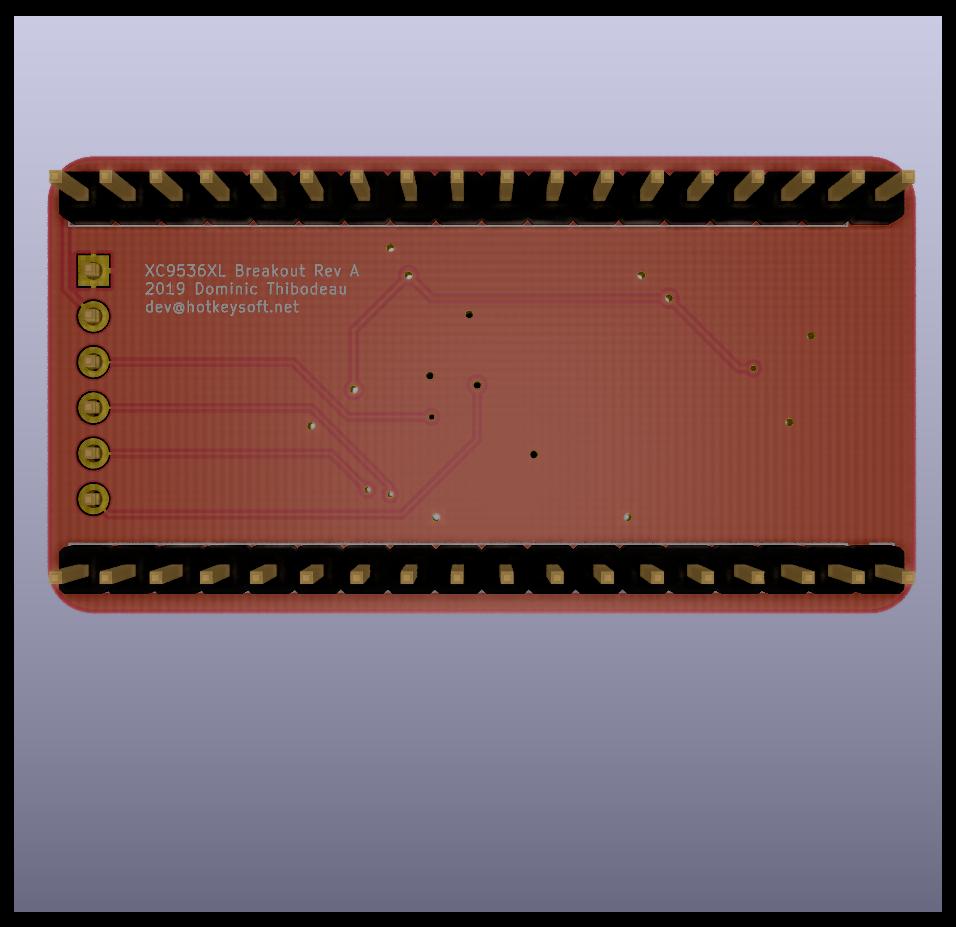

| Front | Back |

|---|---|

|

|