This project implements a generic function generator in VHDL, designed to be compatible with various FPGAs and compile using Quartus Prime. It adheres to the VHDL 2008 standard, ensuring modern and efficient implementation practices. The function generator comprises modules for generating a diverse range of waveforms, including sine, square, triangular, and sawtooth waves. It is designed with a generic architecture, enabling users to customize parameters such as waveform type, frequency, phase offset, and resolution according to their specific requirements.

- Makefile

- src/

- test/

To simulate the VHDL files using GHDL, follow these steps:

- Ensure you have GHDL installed.

- Open a terminal.

- Navigate to the project directory.

- Run

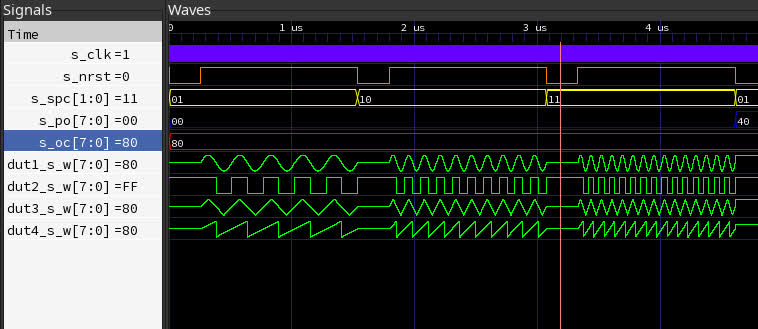

maketo compile and execute the testbenches. - After simulation, waveform files (

*.vcd) will be generated in current directory.

To synthesize the VHDL files using Quartus Prime, follow these steps:

- Open Quartus Prime.

- Create a new project and add the VHDL files (

*.vhd) from thesrcdirectory. - Ensure that the VHDL standard is set to VHDL 2008.

- Set the top-level entity to

top.vhdto specify the main entity of your design. - Compile the project.

- Perform design analysis and synthesis.

- Configure the FPGA device with the generated programming file (e.g.,

.sofor.pof).

This project is compatible with Altera FPGAs and has been tested with Quartus Prime. The VHDL files are written with VHDL 2008 syntax, so it's important to configure the synthesis tool (such as Quartus Prime) to support VHDL 2008 features for proper synthesis and implementation.

This project is licensed under the MIT License. See the LICENSE file for details.