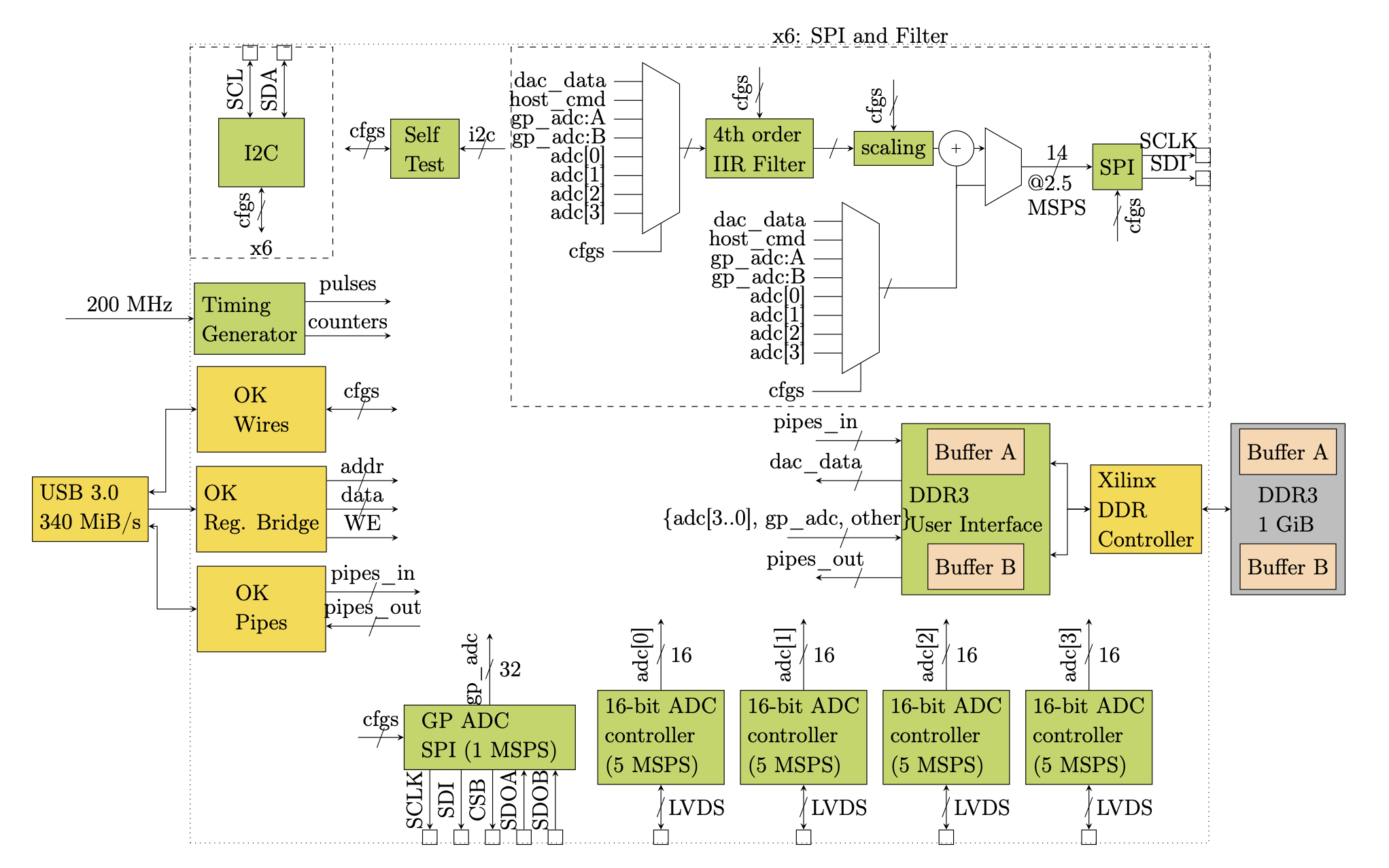

Verilog and Python for a general purpose data acquisition system using an OpalKelly FPGA as the main controller. The Python is designed to be a general purpose approach to interface with multiple peripheral components that contain register maps.

-

Clone the covg_fpga repository with github. This provides the required FPGA bitfile and test code.

-

Install pyripherals with pip

pip install git+https://github.com/lucask07/pyripherals

To use an FPGA and pyripherals:

-

Download FrontPanel from OpalKelly

-

Download Registers.xlsx from the GitHub

-

Create config.yaml with create_yaml and edit fields as needed

>>> from pyripherals.utils import create_yaml

>>> create_yaml()

YAML created at C:/Users/username/.pyripheralsSee Installation Guide for more information.

If this work contributes to your research please cite:

I. Delgadillo Bonequi, A. Stroschein, and L. J. Koerner, “A field-programmable gate array (FPGA)-based data acquisition system for closed-loop experiments,” Review of Scientific Instruments, vol. 93, no. 11, p. 114712, Nov. 2022, doi: 10.1063/5.0121898.

A. Stroschein, I. D. Bonequi, and L. J. Koerner, “Pyripherals: A Python Package for Communicating with Peripheral Electronic Devices,” Journal of Open Source Software, vol. 7, no. 79, p. 4762, Nov. 2022, doi: 10.21105/joss.04762.

This work is partially supported by National Institutes of Health (NIH) R15 grant R15NS116907 to PI L. J. Koerner.

-

The I2C controller is from OpalKelly OpalKelly I2CController (MIT License).

-

The AD7961 controller is from Analog Devices and is free to use / redistribute as long as its used with Analog Devices parts (which must be the case since it does not work if connected to other parts). The Verilog is available within the EVAL-AD7960 evaluation kit software

-

The SPI Controller is from OpenCores.org and is authored by Simon Srot (GPL 2.1 or later license).

-

The wishbone master is written by Dan Gisselquist, Gisselquist Technology LLC. (LGPL, v3)

-

The DDR user interface (ddr_test.v) started with the OpalKelly DDR example provided in the FrontPanel example RAMTester and was significantly modified to support two ports.

- Matplotlib

- numpy

- pandas

We have targeted and tested with the XEM7310-A75 module (Xilinx Artix-7). We have not tested but anticipate reasonable portability to other USB 3 OpalKelly modules including:

- XEM7310MT

- XEM7320

- XEM7305

- XEM7360

Research reported in this repository was supported by the National Institute Of Neurological Disorders And Stroke of the National Institutes of Health under Award Number R15NS116907. The content is solely the responsibility of the authors and does not necessarily represent the official views of the National Institutes of Health.