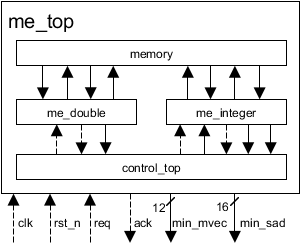

Hardware implementation of Motion Estimation algorithm written in Verilog-HDL. It's currently under development.

- Fullsearch based motion estimation

- Double acuracy, integer acucuracy motion estimation

- No fractional motion estimation

- Template Block: 16x16 pixels

- Search Range : ±24 pixels

- Open

memory/memory.xlsx - Click 'Create Memory' button to create

memory/memory_sw_A.txt,memory/memory_sw_B.txt,memory/memory_sw_C.txt,memory/memory_sw_D.txtfor search range memory andmemory_tb_A.txt,memory_tb_B.txt,memory_tb_C.txt,memory_tb_D.txtfor template block memory - Run

make_tb.sh - You will find the wave file

testbench/***.vcd

- Open

memory/memory.xlsx - Click 'Create Memory' button to create

memory/memory_sw_A.txt,memory/memory_sw_B.txt,memory/memory_sw_C.txt,memory/memory_sw_D.txtfor search range memory andmemory_tb_A.txt,memory_tb_B.txt,memory_tb_C.txt,memory_tb_D.txtfor template block memory - Run

make_mif.shto generate mif files - Open

fpga/fpga_top.qpfin Altera Quartus Prime - Compile it

The Motion Estimation Processor source code is organized as follows:

docs/ documentation

fpga/ fpga related files

memory/ memory dependencies

rtl/ RTL files for Motion Estimation Processor

testbench/ test suites

tools/ tool for creating mif file