GPGPU processor supporting RISCV-V extension, developed with Chisel HDL.

Copyright 2021-2022 by International Innovation Center of Tsinghua University, Shanghai

We are calling for contributors. If you are interested in Ventus GPGPU, please contact yangkx20@mails.tsinghua.edu.cn

“承影”在RVV编译器工具链、验证环境开发和硬件设计方面还有很多不足,如果您有意愿参与到“承影”的开发中,欢迎在github上pull request,也欢迎联系 yangkx20@mails.tsinghua.edu.cn

8月23日线下活动的ppt已经上传到这里。

目前开发中的文档手册在这里,添加了对OpenCL支持所需的改动。2.0版本架构方案尚未确定,如果您在软硬件方面有任何建议,欢迎提issue或邮件联系。

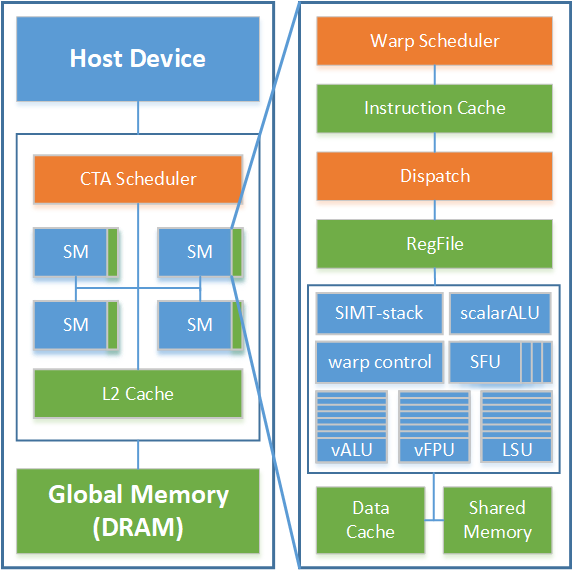

The micro-architecture overview of Ventus(承影) is shown below. Chinese docs is here. English version will come soon.

For ISA simulator and riscv-gnu-toolchain, see ventus-gpgpu-isa-simulator and ventus-riscv-gnu-toolchain

从零开始的配置教程(中文,从WSL和IDEA安装讲起)

The tutorial of Chisel development environment configuration comes from chipsalliance/playground: chipyard in mill :P

- Install dependencies and setup environments:

- Arch Linux

pacman -Syu --noconfirm make parallel wget cmake ninja mill dtc verilator git llvm clang lld protobuf antlr4 numactl - Nix

nix-shell - Ubuntu

apt-get install make parallel wget cmake verilator git llvm clang lld protobuf-compiler antlr4 numactl

curl -L https://github.com/com-lihaoyi/mill/releases/download/0.10.8/0.10.8 > mill && chmod +x mill- Init and update dependences

make init

make patch- IDE support

make bsp # generate IDE bsp - to generate verilog file, use

make verilog. The output file isGPGPU_axi_top.v - to run tests, use

make tests. Output waveform file is attest_run_dir

We refer to some open-source design when developing Ventus GPGPU.

| Sub module | Source | Detail |

|---|---|---|

| CTA scheduler | MIAOW | Our CTA scheduler module is based on MiaoW ultra-threads dispatcher. |

| L2Cache | block-inclusivecache-sifive | Our L2Cache design is inspired by Sifive's block-inclusivecache |

| Multiplier | XiangShan | We reused Array Multiplier in XiangShan. FPU design is also inspired by XiangShan. |

| Instructions, Config, ... | rocket-chip | Some modules are sourced from RocketChip |