| 1. Setup SDx | 2. Introduction to SDx | 3. Optimization | 4. RTL Kernel Wizard | 5. Debugging | 6. SDx command line |

Welcome to the XUP SDx tutorial. These labs will provide hands-on experience using the SDx software tools with Xilinx FPGA hardware.

The SDx tools can be run on your local machine, or in the cloud (e.g. AWS or Nimbix).

The tutorial instructions target the following hardware and software:

- SDx 2018.3

- AWS EC2 F1 f1.2xlarge (cloud)

- Alveo U200 (local board, or cloud)

You can build designs locally or in the cloud, and test on hardware locally (if you have an Alveo board) or in the cloud (AWS EC2 F1, Nimbix Alveo U200).

You will learn how to develop applications using the SDx development environment that supports OpenCL/C/C++ and RTL kernels.

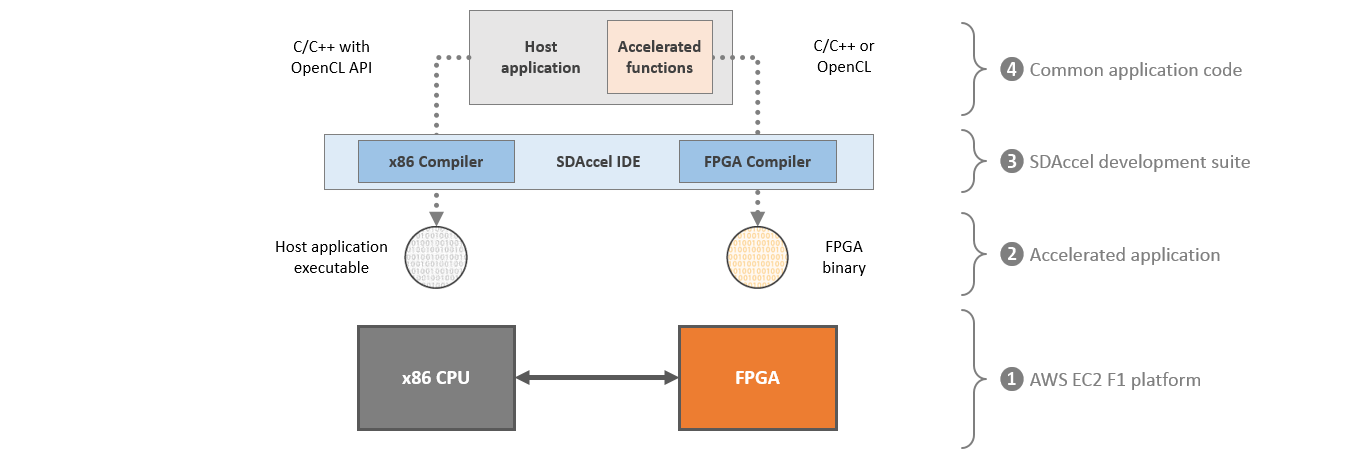

- SDx is the development environment used to create host applications and hardware accelerators. It includes host CPU and FPGA compilers, and profiling and debugging tools.

- The host application can be written in C or C++ and uses the OpenCL API or the XRT (Xilinx Runtime Library) to interact with the accelerated hardware functions running in the FPGA. The accelerated hardware functions (also referred to as kernels) can be written in C, C++, OpenCL or RTL.

It is recommended to complete each lab before proceeding to the next.

-

Setup SDx This will show you how to setup SDx on your own machine, or how to use it in the cloud (instructions are provided for AWS and Nimbix clouds).

-

Introduction to SDx This lab guides you through the steps involved in using a GUI flow to create an SDx project. After creating a project, you will run CPU and hardware emulation to verify the functionality. You will then use an AWS F1 instance to validate the design on F1.

-

Optimization This lab guides you through the steps involved in creating a project and adding a kernel function. After creating a project, you will run CPU and hardware emulation to verify the functionality, analyze various generated reports and then apply techniques both on host and kernel side to improve throughput and data transfer rate.

-

RTL-Kernel Wizard This lab guides you through the steps involved in using a RTL Kernel wizard to wrap a user RTL-based IP so the generated IP can be used in SDx project.

-

Debug This lab will show you how to carry out host application debug, and debug of the hardware kernel.

-

SDx command line This lab guides you through the steps involved in using the SDx command line (using a Makefile) to build and perform CPU and hardware emulation of your design. You will then test the design using FPGA hardware.

When you have setup your instance, go to the first lab Introduction to SDx