✨🐾✨ This project aims to design a Control System for Washing Machine using Verilog HDL.

The washing machine controller has the following functionalities:

-

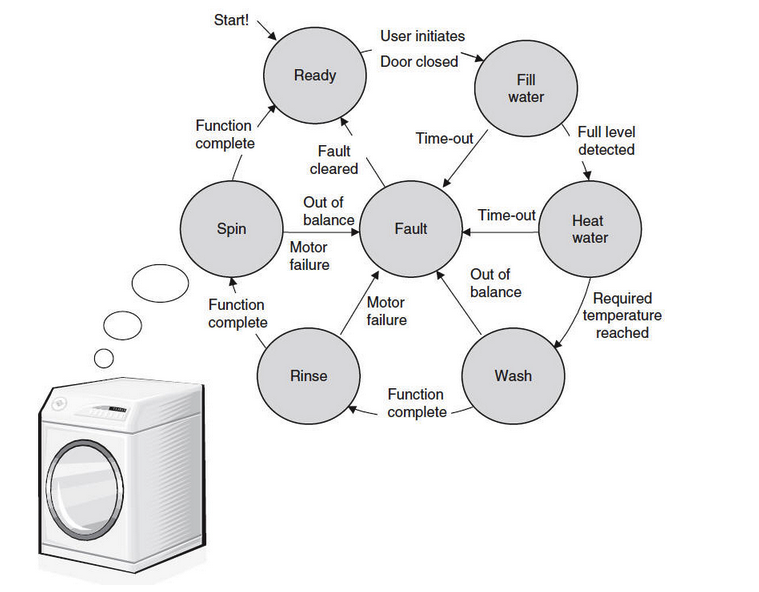

The washing machine has the following states: start, ready, fill water, heat water, wash, rinse, spin and fault.

-

Different time durations are allocated to each mode of operation.

-

Resume washing cycle from the state when:

🚫 the operation is timed out.

🚫 the operation is out of balance.

🚫 motor fails.

The microcontroller is composed of two blocks:

🔹📍 Finite state machine block (controller)

🔹📍 Timer block

The FSM (controller) block receives some signals from the user, from the timer, and other hardware parts such as the door sensor. FSM block output controls the timer block and other hardware components of the washing machine. The FSM has the following states:

- START

- READY

- FILL WATER

- HEAT WATER

- WASH

- RINSE

- SPIN

- FAULT

State transitions take place according to the timing control signals generated by the timer block and inputs given to a particular state. The processing in the next state depends on outputs produced in the previous state.

The timer block generates the correct time periods required for each cycle after it has been reset. The timer block gives the correct time signals once certain count values have been achieved.

Once the washing process starts, the state transitions take place according to the control signals generated by the Timer unit.

-

Once the coin is inserted, the FSM will go to the READY state. If in READY state the process is canceled, the coin is returned as the washing process has not yet started and the FSM returns to the START state. But once the washing process starts, cancellation results in loss of the coin.

-

The FSM has been designed to handle accidents such as motor failure in the middle of a cycle. The machine goes to READY stage in such situations.

-

The control signal to activate the water intake is generated during both the FILL WATER and RINSE states, as both the operations require a fresh intake of water.

-

In the last state, SPIN is completed, the FSM transits back to START state to take orders for the new wash cycle.

This project needs Icarus-Verilog and a VCD viewer.

- Icarus-Verilog can be installed via Homebrew :

$ brew install icarus-verilog - Download Scansion from here.

- Clone the repository.

$ make simulate- compiles design+TB & simulates the verilog design.$ make display- displays waveforms.