RiSC stands for Ridiculously Simple Computer. It is an ISA used for teaching purposes, based on the Little Computer (LC-896) ISA developed by Peter Chen at the University of Michigan.

-

16-bit architecture

- 16 bit registers

- 16 bit ALU

- 16 bit Data bus

- 16 bit Address bus

-

8 registers

r0is always 0- All other registers

r1-r7are general purpose

-

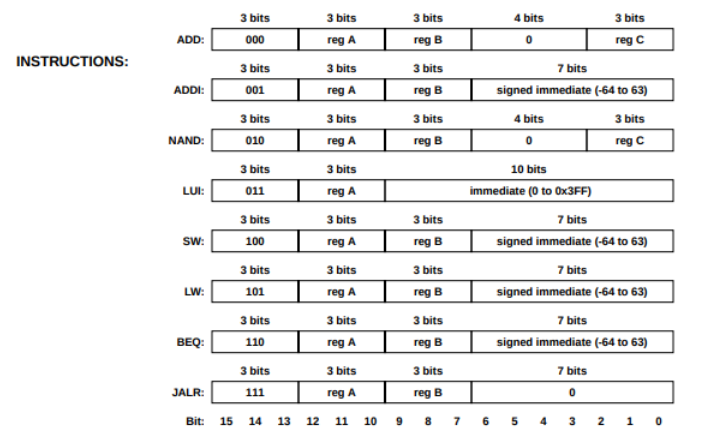

Above 3 images are from the RiSC-16 ISA reference (in references)

The following naming convention is followed in the verilog code :

| Prefix | Meaning |

|---|---|

i_ |

Input port |

o_ |

Output port |

p_ |

Parameter (or localparam) |

r_ |

Register |

w_ |

Wire |

s_ |

State definitions (as localparam) |

The following legend is followed for all diagrams in the documents. (all diagrams were made using drawio)

-

Implementation of a simple non-pipelined version

-

RTL code written in verilog

-

Constrained random verification using system verilog

- Reference models of sub-components

- Testing by comparing results of reference model and RTL design using constrained random stimulus

-

Formal verification using symbiyosys

- Proved register file and data memory using k-induction and bmc

-

Documentation : ./single_cycle/readme.md

- Tools for RiSC-16 written in python

- Assembler

- Random instruction generator

- For documentation and usage, go to ./utils/readme.md