Цифровой синтез: RISC-V / под общ. ред. А. Ю. Романова. – М.: ДМК Пресс, 2024. – 628 с. ISBN 978-5-93700-282-2

Авторы: Американов А. А., Антонов А. А., Барабанов А. В., Жельнио С. Л., Зунин В. В., Иванец С. А., Коробков М. А., Куделина Л. А., Кудрявцев И. А., Маршутина Е. Н., Панчул Ю. В., Романов А. Ю., Романова И. И., Телятников А. А., Шуплецов М. С.

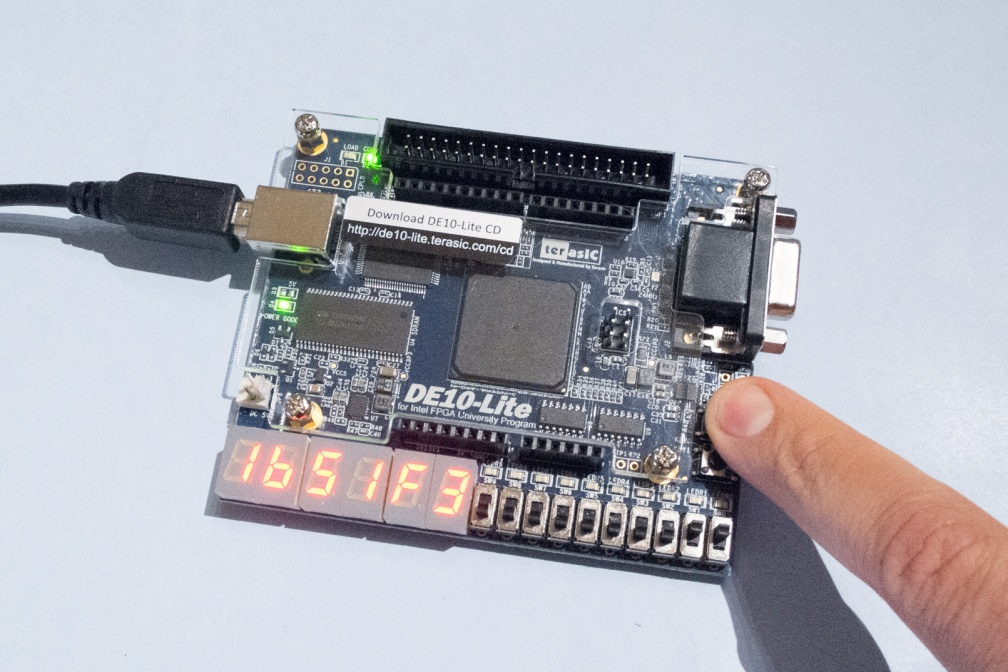

Книга представляет собой расширенный практический курс, ориентированный на язык Verilog и обеспечивающий возможность выполнения практических задач на дешевых отладочных платах Terasic DE10-lite. Этот практикум дополняет и объединяет теоретические курсы по цифровой логике, языкам описания аппаратуры, компьютерной архитектуре и микроархитектуре, а также подготавливает студентов к работе с промышленными процессорными ядрами, к созданию специализированных вычислителей (например, ускорителей нейросетей) и курсов VLSI по проектированию массовых микросхем ASIC.

Материал каждой главы можно изучать автономно. В конце глав приводятся вопросы и упражнения, позволяющие преподавателям встраивать данный материал в любой учебный курс, а читателям книги – закрепить новые знания, самостоятельно выполнив предлагаемые задания.

Издание предназначено для студентов технических вузов, разработчиков аппаратно-программных систем, а также специалистов в области прикладной математики, интересующихся алгоритмами САПР.

https://dmkpress.com/catalog/electronics/circuit_design/

Для клонирования репозитория необходимо указать опцию --recurse-submodules для клонирования подмодулей, исползованных в репозитории.

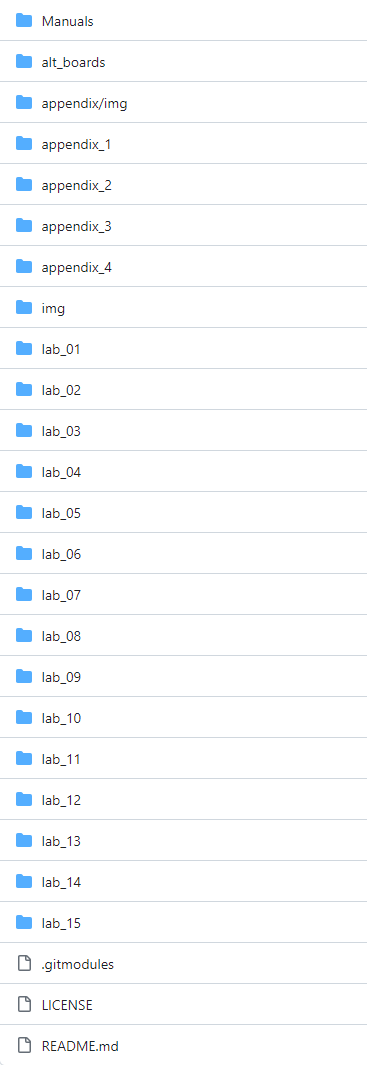

Репозитарий содержит исходные коды к каждому практическому примеры в книге и разбиты на главы.

Все коды адаптированы под выполнение на дешевой плате Terasic DE10-lite,

но мы приветствуем комиты портов под другие платы alt_boards.

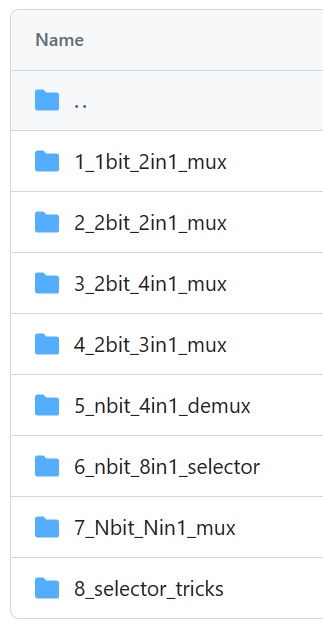

Каждая папка соответствует определенной практической работе и содержит ReadMe файл. В дополнении к нему могут содержаться поддиректории doc, pkg, img, src.

Все они содержат полезные материалы к работе. Главной является папка src, где лежат примеры исходных кодов, которые разбираются в главах книги.

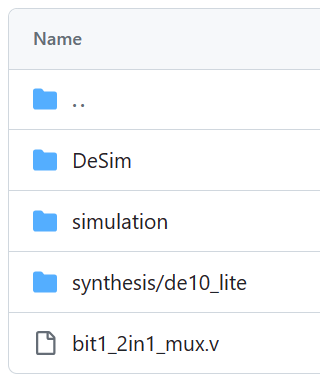

Каждый пример содержит файл верхнего уровня иерархии

и папки со скриптами для симуляции и синтеза проекта.

Предполагается, что при прочтении книги вы готовите отчет по каждой главе.

Вы читаете главу исполняя практические примеры приведенные в главе. А в отчете описываете ход выполнения работы. Если в главе есть дополнительные задания для самостоятельной работы, их надо выполнить и описать ход выполнения в отчете. Исходные коды документируются. А все примеры выполняются на плате.

Таким образом будет достигнут максимальный эффект от освоения книги.

Данное приложение позволяет выполнять компиляцию и моделирование кода на языке Verilog, обеспечивая взаимодействие с виртуальной платой через графический интерфейс, т. е. не задействуя физическое оборудование. Интерфейс предоставляет основные возможности платы DE1-SoC.

Примеры исходных кодов, которые разбираются в книге, адаптированы под это приложение и находятся в соответствующих папках с названием DeSim. В каждой из них лежит пакетный файл make_desim_project.bat, который автоматически собирает проект под запуск в DESim.

Руководства по DESim, переведенные на русский язык, находятся в папке Manuals данного репозитария:

https://github.com/RomeoMe5/ddlm_riscv/tree/master/Manuals

Оригинальные руководства по DESim: https://github.com/fpgacademy/DESim/releases

Любые ошибки, неточности или исправления, а также предложения о сотрудничестве присылайте на почту a.romanov@hse.ru.