The 74LS, 74HC, 74HCT family of chips in Verilog for Electronic Design Automation

Fully validated by test bench · Parametrized code · DELAY parameters for timing simulation

IceChips is built to support the Icestudio and FPGAwars manifesto:

<Open Hardware driven by Open Source>

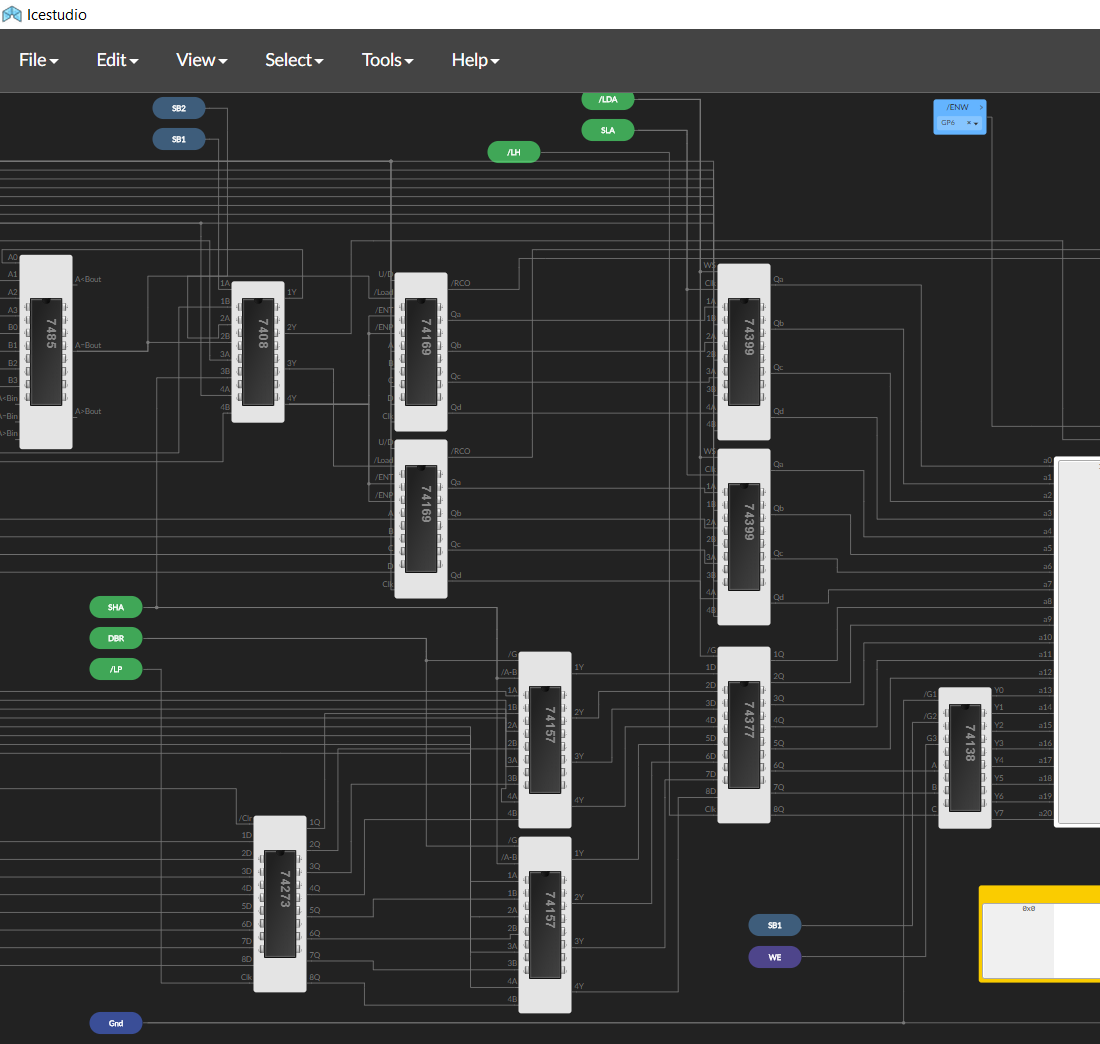

The easiest way to use these devices is download the collection and open it in the Icestudio design environment.

In Icestudio, go to Tools > Collections > Add and select the downloaded .zip file. Place and wire up your components, run and test the result. There's a variety of ways to provide inputs and view outputs; but no need for actual parts, wires or power supply.

Alternatively, you can download an individual device (74xx.v file) and use it in your own simulation in Verilog. This is the way to go if you wish to set the parameters for # bits, # inputs per gate, # blocks in a device.

See the Index to browse devices.

They're digital logic: Gates, multiplexers, counters, registers, adders, multipliers and more. See Wikipedia full list.

Welcome to virtual breadboarding.

Icestudio provides circuit simulation (for digital circuits) that's arbitrarily scalable. Explore, build and create, but most importantly, get near-instant feedback in testing your real hardware design. Each time you add a new input or a gate, or an LED, hit "Build" and "Upload". In the parlance of a silicon fab, you've gone through a "spin". But you're actually programming a reusable and fairly inexpensive FPGA.

CAD-style layout using drag & drop

-> Full Verilog model

-> Validation of design rules & connectivity

-> Synthesis of circuit

-> Bitstream to FPGA

-> Live circuit to test or put in-situ

It's done with entirely open source tools (the IceStorm toolchain); and most of the magic is due to the representation in Hardware Description Language, i.e. Verilog:

-

Once you have a system fully modelled in HDL, you have everything: The HDL is used to generate hardware in any way you require, in a process called logic synthesis;

-

The toolchain can synthesize the circuit onto an expanding selection of FPGAs; see Icestudio for details;

-

Icestudio's graphical editing, with internal Verilog, makes it easy and explicit to work with the hierarchy and layering paradigm provided by Verilog; this promotes compositional design - being intentional about the boundary, the spec and the validation of each of your modules - which in turn means scalability and testability.

A test bench accompanies every device (74xx-tb.v file with 74xx.v file) and the tests are run automatically. You can click on the "tests" badge below the main title at top of page to see the logged results.

Tests are a definitive feature of the library. Count on full test coverage as the library expands going forward.

You have to "trust but verify" when scaling up a hardware design from lower-layer components.

Test benches

IceChips tests must be:

- Comprehensive

- Meaningful (each test adding value)

- Annotated with descriptions

- Self-checking

The test benches are for documentation and transparency and create a kind of audit trail. That's in addition to their role in correctness!

Self-checking: Each test gives a Pass/Fail result. It does this by using an "assert" statement, that logs a failure message if the stated condition (at the output) is not met. The tests are not just doing a demonstration run of the device by way of a waveform output - although they do that also.

For open source purposes and community contribution: IceChips guidelines around test benches.

IceChips is actually built around validation end-to-end. The code files are generated by script, from a template, for reliably validated code and .ice components.

Here's an overview, with a visual that shows the structure of the code files:

Validation scheme and contract for the Verilog code

Direct to the contract

Running the tests on your machine

The test benches can be run using the open source simulator Icarus Verilog: Installation, Getting Started.

With it installed, you can run a command like the following that specifies the required input files and one output file (.vvp):

> iverilog -g2012 -o7400-tb.vvp ../includes/helper.v ../includes/tbhelper.v 7400-tb.v 7400.v

It then requires a second step: Run the Icarus Verilog simulator/runtime to see the tests run. This will show the results logged to the console:

> vvp 7400-tb.vvp

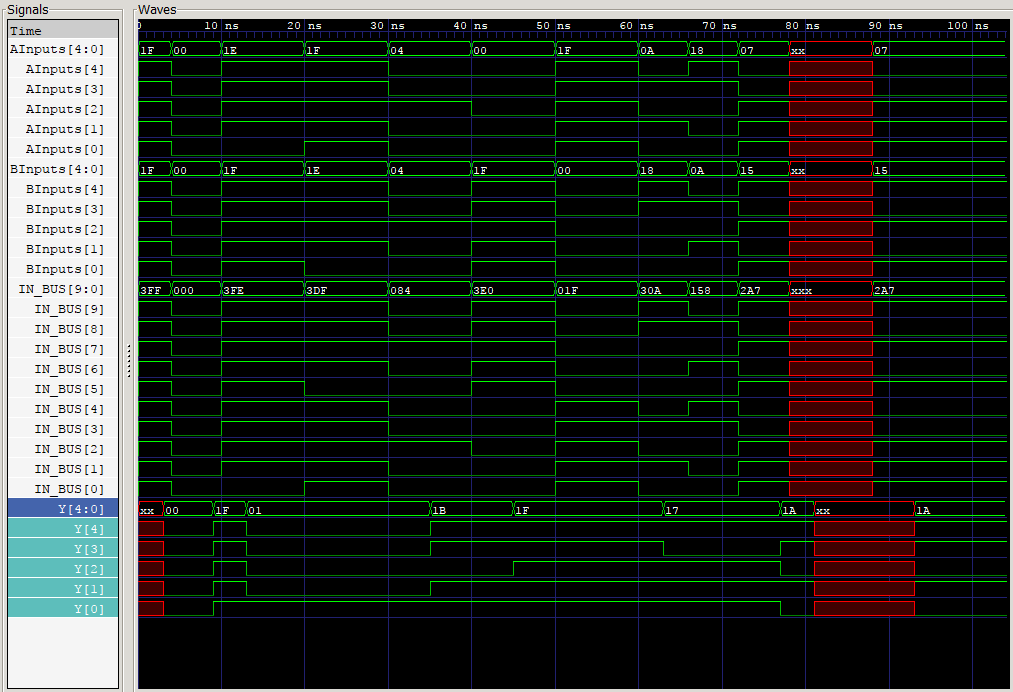

If you're interested in looking closer, the "vvp" run stores all signal and timing data in a .vcd file, so you can see the run as a waveform using GTKWave viewer: Installation, Getting Started.

With GTKWave installed, just click on the .vcd file.

To brush up on digital logic design, or get started with an EDA flow to create, test out and tape-out your project:

Topics to get started

- Combinational Circuit versus Sequential Circuit

- RTL Description · Register Transfer Level Description

- HDLs · Hardware Description Languages

- Logic Simulation

- Logic Synthesis

- Logic Friday (Program)

- Espresso Logic Minimizer (Program)

- EDA · Electronic Design Automation

- FPGAs · Field-Programmable Gate Arrays

Clarification about this design flow versus PCB (Printed Circuit Board) flow:

PCB design flow

Are you planning to populate your components onto a custom PCB?

You have a head start from simulating and testing your design, that's for sure. You know your digital circuit meets all its specs.

However, you'll have to get into a different workflow to create a PCB: A different type of visual editing ("schematic capture"); placing, routing and design of layout for manufacture; verification of design rules for manufacture (this time for geometric/electrical properties).

Note: Having said that, using 74xx standard parts will set you up well for using PCB software, since the parts are well-known and modelled for geometric/electrical properties.

The following keywords are related to PCBs and are not part of the present workflow:

- Ngspice

- SPICE

- Eagle

- Gerber format

- Most software programs that have CAD in them (KiCAD) and the ones that have PCB in them (LibrePCB)

- gEDA suite (for the most part)

www.homebrewcpuring.org · Amazing Homebrew CPUs

Hackaday Homebrew CPU projects · More Homebrew CPUs

FPGAwars list of projects developed with Open Source FPGAs, including CPUs

OSHWA · Open Source Hardware Association and their project list

Juan González-Gómez [@Obijuan], Jesús Arroyo Torrens, Salvador E. Tropea, Democrito · for Icestudio collections

Warren Toomey [@DoctorWkt] · for inspiration because he builds real CPUs, and for using early versions of these devices

Eddie Hung [@FPGeh] · for Yosys advice and feedback

digitaljs.tilk.eu Marek Materzok [@tilk] · for helpful feedback and has an amazing convenient simulator "DigitalJS Online"

www.edaboard.com "mrflibble" · provided solution for 2-dimensional inputs to a module

"Inside the vintage 74181 ALU chip" Ken Shirriff · invaluable info on the 74181 and a fabulous simulator in the browser

Marcus Lindholm · SVG graphic design help

www.msarnoff.org/chipdb Matt Sarnoff · chip and pin info

"TTL_74xx_DIL.m4" Thomas Nau, "diplib" in PCB for Linux distribution · chip and pin info

www.referencedesigner.com/tutorials · practical intro to Verilog with examples, tutorials, quizzes

www.doulos.com/knowhow · intro to design and concepts in Verilog

www.verilogpro.com · intro to generate loops and elaboration

Icestudio and Apio built on top of IceStorm, Yosys, nextpnr

Yosys synthesis by Claire Wolf

Icarus Verilog simulator by Stephen Williams

GTKWave for viewing waveforms

© 2018-2024 Tim Rudy