A place to keep my synthesizable verilog examples.

Table of Contents

- OVERVIEW

- BASIC CODE

- COMBINATIONAL LOGIC

- SEQUENTIAL LOGIC

- COMBINATIONAL LOGIC

- ALUs

- DATA OPERATORS

- DECODERS & ENCODERS

- MULTIPLEXERS & DEMULTIPLEXERS

- FPGA DEVELOPMENT BOARDS

- BUTTONS

- SEQUENTIAL LOGIC

- ARBITERS

- COUNTERS

- FINITE SATE MACHINES

- MEMORY

- REGISTERS

- SHIFTERS

- SYSTEMS

- MICROPROCESSORS

- PIPELINES

Documentation and Reference

- verilog cheat sheet

- iverilog is a free tool for simulation and synthesis

- GTKWave is a free HDL waveform viewer

- xilinx vivado is a complete IDE for synthesis and analysis of HDL designs

- digilent ARTY-S7 is a FPGA development board

- My Master's Thesis has an explanation of HDLs and how they fit into frameworks

- My Master's Thesis also has my design of a programable_8_bit_microprocessor

- This repos github webpage built with concourse

Each example uses iverilog to simulate and GTKWave to view the waveform. I also used Xilinx Vivado to synthesize and program these verilog examples on a Digilent ARTY-S7 FPGA development board.

I declare my ports as follows because that's what the synthesis tools want. Who am I to argue.

module NAME (

input a, // Input A

input [7:0] b, // Input B

output reg [3:0] y); // Output YAlso, I would stay away from asynchronous design. It can have problems when you synthesize to an FPGA.

// DO THIS

always @(posedge clk) begin

if (~reset) begin

...

// NOT THIS

always @(posedge clk or negedge reset) begin

Each example has the following 4 files,

*.v- The verilog code files(s)*.vh- A header file listing the included verilog files*_tb.v- The verilog testbench code*_tb.tv- Test vectors used with the testbench

The artifacts created are,

*_tb.vvp- The verilog compiled code to be used by the simulator*_tb.vcd- The dump of the waveform data*_tb.gtkw- The GTKWave saved waveform

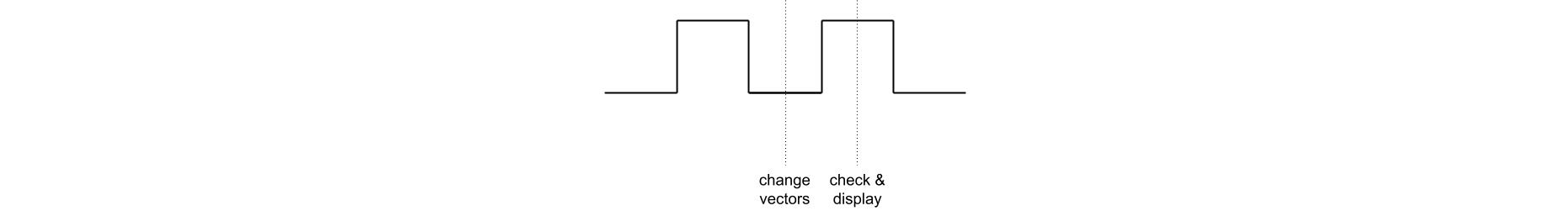

Where the testbench structure is,

-

COMBINATIONAL LOGIC

-

2-input AND gate used in my programable_8_bit_microprocessor.

-

4-input NAND gate used in my programable_8_bit_microprocessor.

-

2-input NOR gate used in my programable_8_bit_microprocessor.

-

NOT gate used in my programable_8_bit_microprocessor.

-

2-input OR gate used in my programable_8_bit_microprocessor.

-

2-input XOR gate used in my programable_8_bit_microprocessor.

-

-

SEQUENTIAL LOGIC

-

A sr (set ready) latch which is level-triggered that can be set and reset. The latch forms the basic building block of other types of latches and flip-flops.

-

A sr (set ready) flip-flop which is pulse-triggered can be set and reset.

-

A jk flip-flop which is pulse-triggered can be set, reset and toggled. This has a race condition when clock is high.

-

A pulse-triggered jk flip-flop (cascading) can be set, reset and toggled.

-

jk_flip_flop_pos_edge_sync_clear

A posedge-triggered jk flip-flop with synchronous clear used in my jeff_74x161.

-

A t flip-flop which is pulse-triggered can be toggled. This has a race condition when clock is high.

-

A d flip-flop which is pulse-triggered can save input data on output.

-

A pulse-triggered d flip-flop (cascading) can save input data on output.

-

A posedge-triggered d flip-flop with synchronous enable used in my jeff_74x377.

-

-

ALUs

-

4-bit alu (arithmetic logic unit) and function generator. Provides 16 binary logic operations and 16 arithmetic operations on two 4-bit words. Based on the 7400-series integrated circuits used in my programable_8_bit_microprocessor.

-

-

DATA OPERATORS

-

A 2-bit full-adder.

-

A 2-bit half-adder.

-

-

DECODERS & ENCODERS

-

Encoder - Eights inputs (1 hot) encodes to output.

-

Decoder - Three inputs decodes to 1 of 8 outputs (hot).

-

Combining the encoder_8_3 to the decoder_3_8 to prove the input will equal the output.

-

-

MULTIPLEXERS & DEMULTIPLEXERS

-

Demultiplexer - One input, four outputs.

-

8-line to 1-line data selector/multiplexer. Based on the 7400-series integrated circuits used in my programable_8_bit_microprocessor.

-

Quad 2-line to 1-line data selector/multiplexer, non-inverting outputs. Based on the 7400-series integrated circuits used in my programable_8_bit_microprocessor.

-

Multiplexer - Four inputs, one output.

-

Combining the mux_4x1 to the demux_1x4 to prove the input will equal the output (for the selected output).

-

-

BUTTONS

-

A few different ways to use buttons on a FPGA development board.

-

-

ARBITERS

-

A three level priority arbiter with asynchronous reset.

-

-

COUNTERS

-

Synchronous presettable 4-bit binary counter, asynchronous clear. Based on the 7400-series integrated circuits used in my programable_8_bit_microprocessor.

-

-

FINITE STATE MACHINES

-

Recognize the pattern 00110 in a serial stream. Output depends on current state and current inputs.

-

Recognize the pattern 00110 in a serial stream. Output depends on current state only.

-

-

MEMORY

-

Single-port synchronous RAM.

-

Dual-port synchronous RAM.

-

Dual-port asynchronous RAM using two different clocks.

-

A synchronous fifo using dual-port synchronous RAM.

-

An asynchronous fifo using dual-port asynchronous RAM.

-

A synchronous lifo using dual-port synchronous RAM.

-

-

REGISTERS

-

8-bit register, clock enable. Based on the 7400-series integrated circuits used in my programable_8_bit_microprocessor.

-

A simple 8-bit register with synchronous load and clear.

-

-

SHIFTERS

-

A 4-bit left shift register.

-

-

MICROPROCESSORS

-

programable_8_bit_microprocessor

A programable 8-bit microprocessor. Originally designed in VHDL for part of my master's thesis.

-

-

PIPELINES

-

A simple pipeline.

-