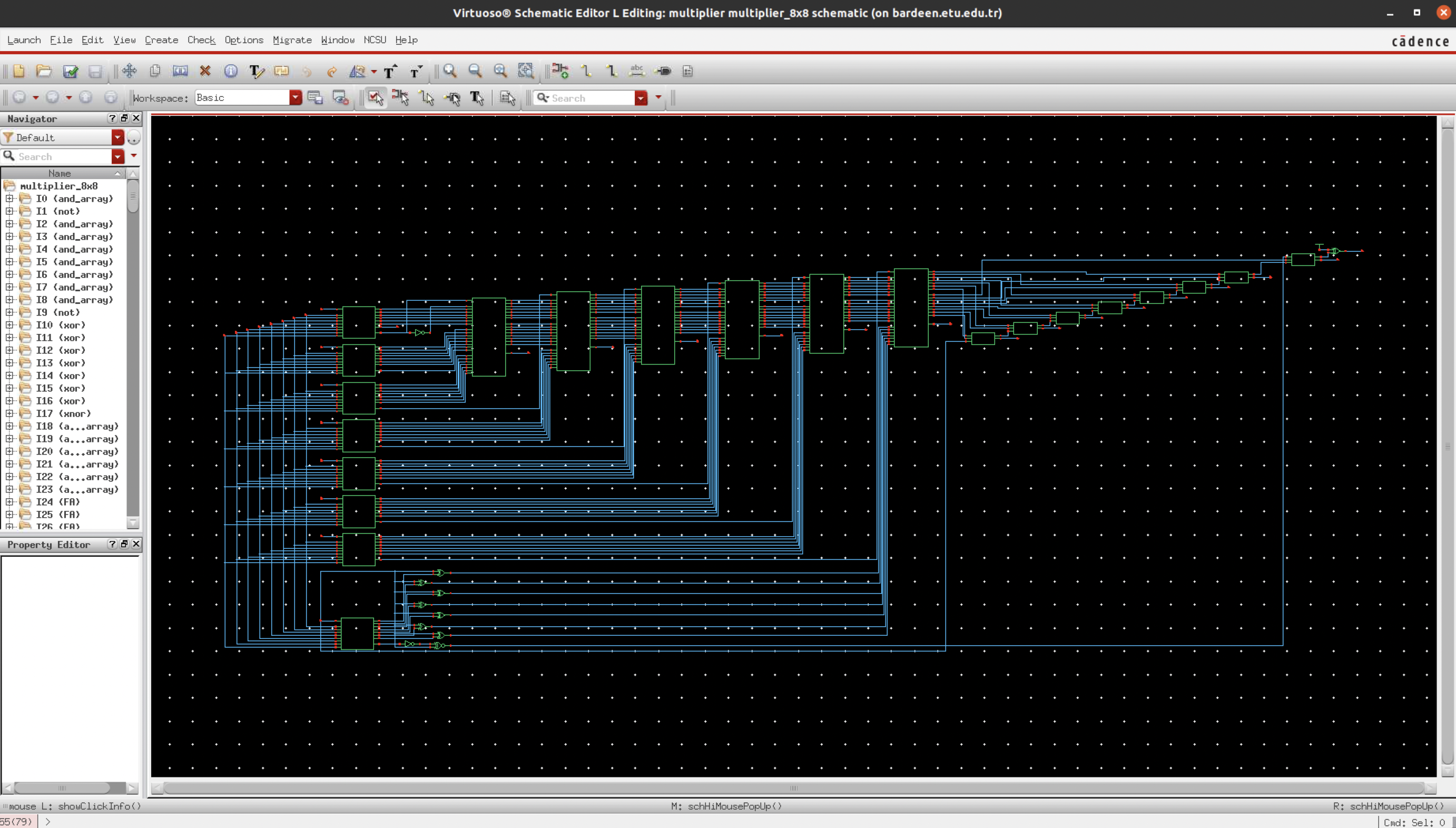

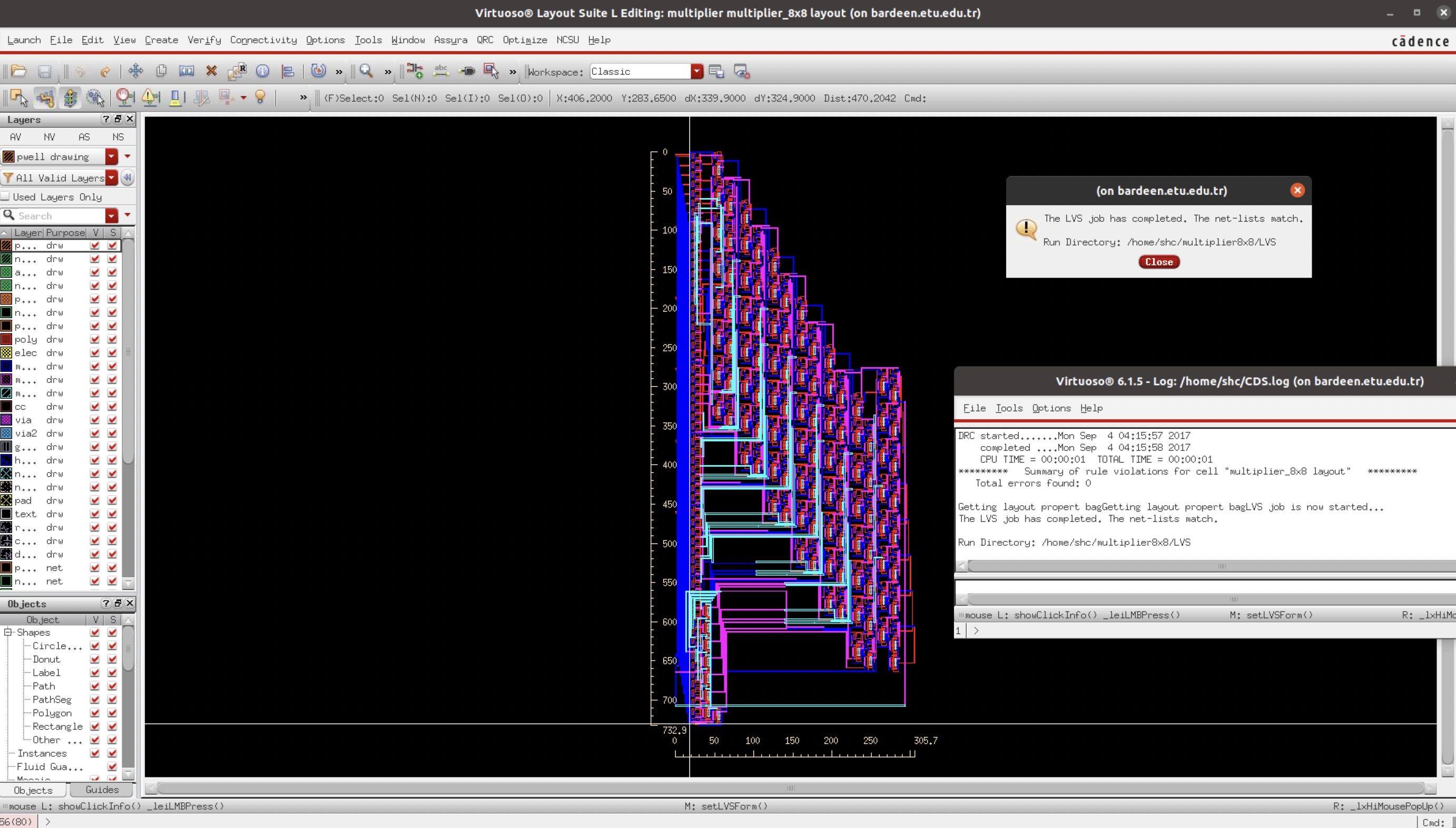

8bit x 8bit Signed Wallace Tree Multiplier 600nm CMOS VLSI Design (verilog + schematic + layout)

Designed in Cadence Virtuoso using open source NCSU CDK 600nm (ami06) process.

Used gate level rtl code borrowed and modified (modularized for easy layout) from Design-of-various-multiplier-Array-Booth-Wallace- repository.

The project is described detailed in the report. (in Turkish)

For using project in Cadence Virtuoso:

cd cadence-project

virtuosoVarious screenshots -from gates to multiplier schematic and layouts- can be found in scrs directory.