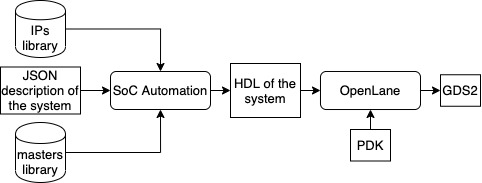

A truly no man in the loop SoC generator.

SoCGen automates SoC design through taking JSON input and generating verilog HDL for the SoC.

We're working on the integration with OpenLane to generate the final GDS2.

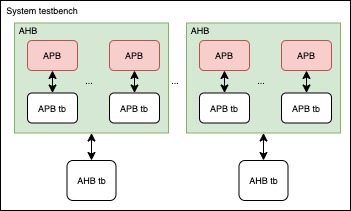

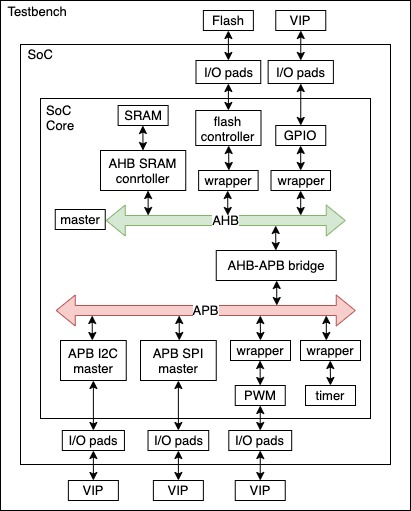

Currently we support AMBA AHB-Lite for the high-speed (main) bus and APB for the low speed peripherals bus.

This instruction will get you a copy of the project up and running on your local machine for development and testing purposes.

% git clone https://github.com/habibagamal/SoC_automationIf you need help with how to run the program

% node ./src/sys_gen.js -help To generate the full SoC .v files

% node ./src/sys_gen.js -soc <soc.json> -mastersLib <masters_lib.json> -IPlib <ip_lib.json> -subsystem <subsystem.json> -outDir <output directory> - Omit any fields you don't need in the above command.

- If there are no subsystems or real masters, you can ommit "-subsystem <subsystem.json>" or "-mastersLib <masters_lib.json>", respectively, from the command.

- You can use this shell script to run SoCGen, run iverilog, then open scansion waveform viewer

For instructions on how to write the JSON file for:

- the masters library: check this

- the IPs library: check this

- the system: check this

- the subsyetem: check this

- systems: contains soc examples

- IPs: contains JSON for IPs library and verilog files for open-source IPs

- masters: contains JSON for masters library and master-related files

- src: contains source code

- JSON_format_doc: contains documentation for JSON format

- Images: contains images used in README

- The page field is used as the base address of buses, AHB slaves and subsystems.

- The subpage field is used as the base address of slaves on APB

- The peripherial field is used as the slave's register offset

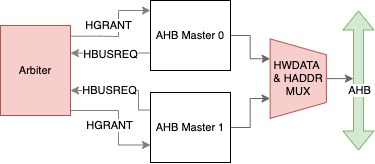

- Having multiple masters (tested on dummy masters)

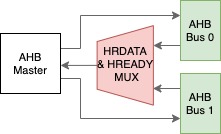

- Having multiple buses connected to the same master

- Having multiple APBs on the same AHB

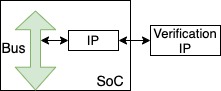

- Using created and open source verification IPs for testing

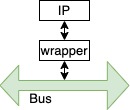

- Using IPs that are not APB or AHB compatible

- Having soft IPs and hard IPs

- Having I/O pads library that is not technology specific (for behavioral simulation)

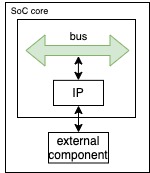

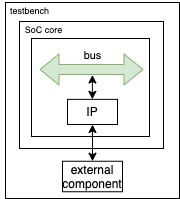

- Specify the placement levels of external components (testbench or soc_core)

- Auto-generating self-checking testbench

- Generating hierarchicial testbenches

This diagram represents this example

Go here to download Arm Cortex M0, M3 files

- Arbiter taken from here

- Datasheet generation

- Check this poster and video presented in DAC 2020 Young Fellowship Program about the project

- Check this presentation, slides and paper presented in Workshop on Open-source EDA Technology (WOSET) 2020 collocated with International Conference on Computer Aided Design (ICCAD) 2020

- Amr Gouhar agorararmard

- Habiba Gamal habibagamal

- Mohamed Shalan shalan