4-bitová aritmeticko-logická jednotka se dvěma vstupy A a B a výstupem Y s přenosem C. Jednotka může provádět 16 různých operací (viz tabulka).

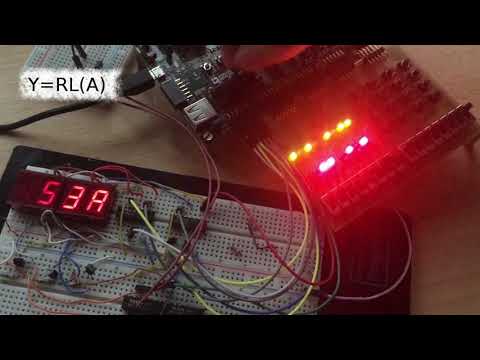

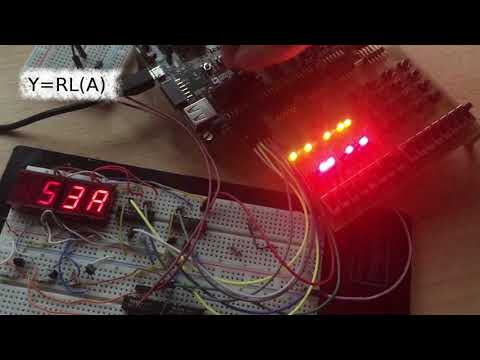

Jednotce lze ručně nastavit vstupní příznak carry, který je u některých operací použit. Výsledná data (včetně vstupů) jsou zobrazena na šestnácti LED diodách a také na čtyřmístném sedmisegmentovém displeji. Všechny vstupní hodnoty se nastavují pomocí přepínačů, které jsou umístěny na externí rozšiřující desce společně s LED diodami.

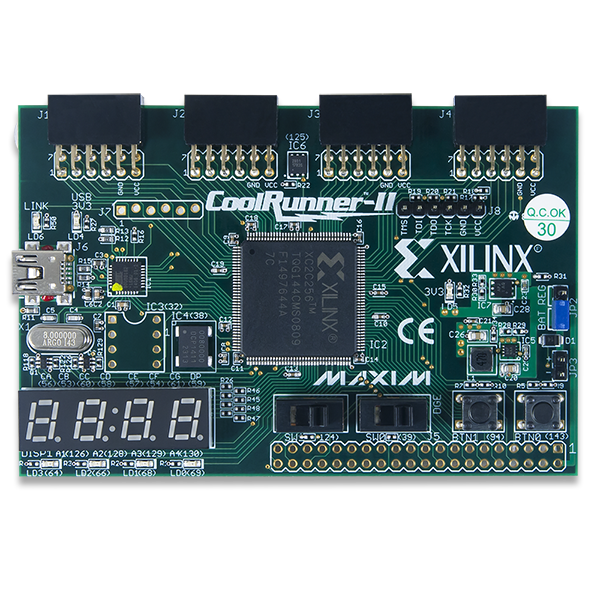

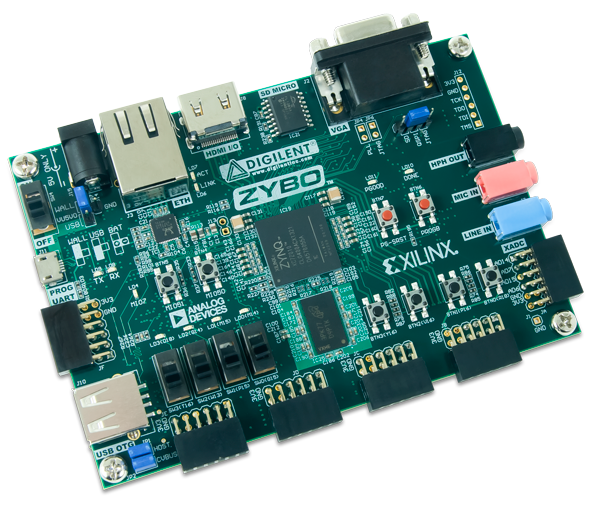

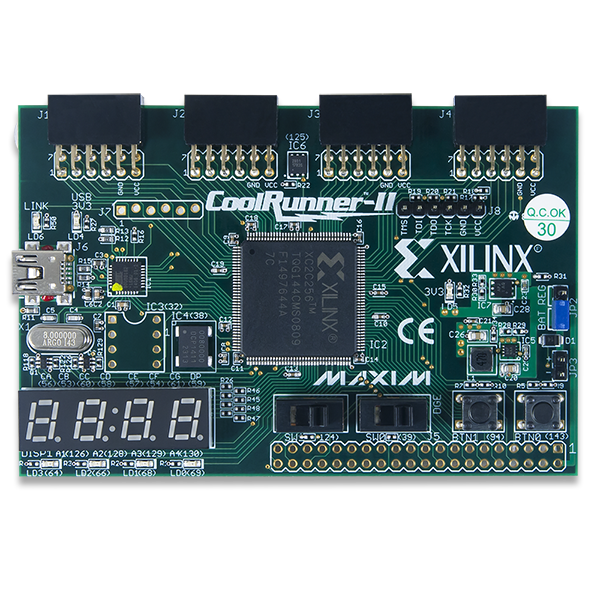

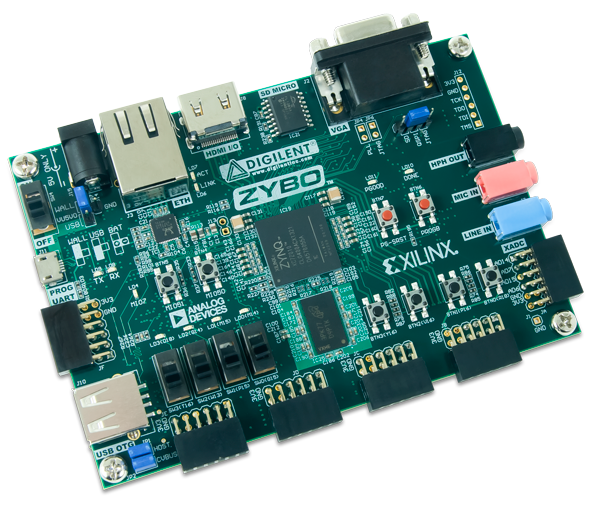

Vývoj probíhal na vývojových deskách CoolRunner-II (CLPD) a Zybo (FPGA). Obě desky jsou od firmy Digilent. Program běží na obou deskách nezávisle, pouze na desce Zybo je nutné snížit vstupní hodinový kmitočet (na 10 kHz) a invertovat výstupy (carry, carry_in, parity).

CoolRunner-II Starter Board [1]

Zybo Zynq-7000 ARM/FPGA SoC Trainer Board [2]

Rozšiřující deska s tlačítky, přepínači a LED diodami

ALU jednotka s vlastní sadou početních/logických/binárních operací, viz např. 74181

Zapojení ALU jednotky s deskou Zybo

Schéma externího hardware připojeného k desce Zybo. Vlevo displej, vpravo LED diody a přepínače.

| Řídící signál | Funkce | Popis |

| 0x0 | Y = A + B | Součet |

| 0x1 | Y = A - B | Rozdíl |

| 0x2 | Y = A + 1 | Inkrementace |

| 0x3 | Y = A - 1 | Dekrementace |

| 0x4 | Y = A + B + C | Součet s přenosem |

| 0x5 | Y = A - B - C | Rozdíl s přenosem |

| 0x6 | Y = A or B | Logický součet |

| 0x7 | Y = A and B | Logický součin |

| 0x8 | Y = A xor B | Exkluzivní logický součet |

| 0x9 | Y = not A | Logická negace |

| 0xA | Y = A >> 1 | Rotace vpravo |

| 0xB | Y = A << 1 | Rotace vlevo |

| 0xC | Y = (A + C) >> 1 | Rotace vpravo s přenosem |

| 0xD | Y = (A - C) << 1 | Rotace vlevo s přenosem |

| 0xE | Y = A'H <=> A'L | Přehození nejvyššího a nejnižšího čtvrbytu |

| 0xF | Y = A mul B | Součin |

| Sčítačka |

|

Numericky sečte hodnoty na vstupech A, B a výsledek uloží do Y. Příznak přenosu je uložen do C. Vstupní příznak přenosu C je ignorován. |

| Odčítačka |

|

Numericky odečte hodnotu na vstupu B od vstupu A a výsledek uloží do Y. Příznak přenosu je uložen do C. Vstupní příznak přenosu C je ignorován. |

| Inkrementace |

|

Numericky inkrementuje hodnotu na vstupu A o jedničku. Příznak přenosu je uložen do C. Vstupní příznak přenosu C je ignorován. |

| Dekrementace |

|

Numericky dekrementuje hodnotu na vstupu A o jedničku. Příznak přenosu je uložen do C. Vstupní příznak přenosu C je ignorován. |

| Sčítačka s přenosem |

|

Numericky sečte hodnoty na vstupech A, B a výsledek uloží do Y. Příznak přenosu je uložen do C. Vstupní příznak přenosu C je přičten k výsledku Y. |

| Odčítačka s přenosem |

|

Numericky odečte hodnotu na vstupu B od vstupu A a výsledek uloží do Y. Příznak přenosu je uložen do C. Vstupní příznak přenosu C je odečten od výsledku Y. |

| Logický součet |

|

Provede logický součet hodnot na vstupu A a B. Výsledek uloží do Y. |

| Logický součin |

|

Provede logický součin hodnot na vstupu A a B. Výsledek uloží do Y |

| Exkluzivní logický součet |

|

Provede logický exkluzivní součet hodnot na vstupu A a B. Výsledek uloží do Y. |

| Logická negace |

|

Provede logickou negaci hodnoty na vstupu A. Výsledek uloží do Y. |

| Rotace vpravo |

|

Provede rotaci hodnoty na vstupu A o jeden bit vpravo. Výsledek uloží do Y. Nejnižší bit je uložen do C. Vstupní příznak C je ignorován. |

| Rotace vlevo |

|

Provede rotaci hodnoty na vstupu A o jeden bit vlevo. Výsledek uloží do Y. Nejvyšší bit je uložen do C. Vstupní příznak C je ignorován. |

| Rotace vpravo s přenosem |

|

Provede rotaci hodnoty na vstupu A o jeden bit vpravo. Výsledek uloží do Y. Nejnižší bit je uložen do C. Vstupní příznak C je uložen na nejvyšší pozici. |

| Rotace vlevo s přenosem |

|

Provede rotaci hodnoty na vstupu A o jeden bit vlevo. Výsledek uloží do Y.

Nejvyšší bit je uložen do C. Vstupní příznak C je uložen na nejnižší pozici. |

| Přehození bitů |

|

Provede vzájemné přehození bitů na vstupu A. Výsledek uloží do Y. Shodné s rotací vpravo nebo vlevo o dva bity. |

| Násobička |

|

Numericky vynásobí hodnotu na vstupu A s hodnotou na vstupu B. Výsledek uloží do Y. Příznak C signalizuje, že výsledek obsahuje numerickou hodnotu vyšší než 15. Na výstup Y jsou přivedeny vždy 4 nejnižší bity. |

| Parita výsledku |

|

Signalizuje lichý počet jedniček ve výsledku. |

| Jednotka ovládání displeje |

|

Řídí čtyřmístný sedmi-segmentový displej se společnou anodou. Segmenty displeje jsou aktivní v nule. Frekvence signálu clk musí být nejméně 10 kHz. |

| Výsledná ALU jednotka |

|

Celkové vstupy a výstupy jednotky.

Vstupy number_a a number_b slouží k nastavení čísel se kterými se budou provádět operace. Vstupem control_sig se nastavuje operace, kterou chceme provádět. Hodnoty se nastavují pomocí přepínačů.

Výstupy number_a, number_b, control_sig a alu_result slouží k binární reprezentaci hodnot, použity jsou LED diody.

Výstupy disp_digit a disp_sseg slouží k dekadickému zobrazení hodnot na 7segmentovém displeji.

|

Některé části (disp_mux) jsou doplněné šablony od pana Frýzy [3].

| Celkové zjednodušené | Více podrobné |

|

|

Prezentace ve formátu PDF

Prezentace ve formátu PPTX

- https://reference.digilentinc.com/_media/reference/programmable-logic/coolrunner-ii/cr2-2.png

- https://www.electronicdesign.com/sites/electronicdesign.com/files/uploads/2014/03/104431_fig3-digilent-zybo.png

- https://gitlab.com/tomas.fryza/vhdl-examples