This project presents a 32-bit RISC processor with a memory controller, completed as a 3rd-year group project for the HDL module at the University of Ruhuna, SL. The processor features a streamlined architecture for faster execution times, utilizing Verilog HDL for implementation and ModelSim for simulation.

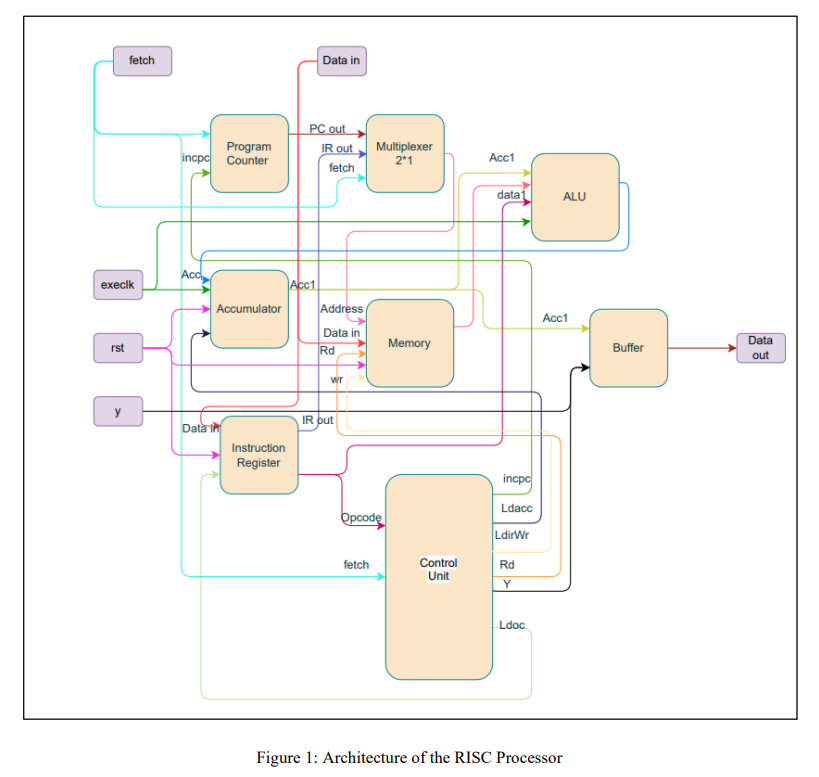

The project aimed to design and implement a Reduced Instruction Set Computing (RISC) processor with a memory controller. The processor is equipped with 15 essential instructions covering arithmetic, logical, data transfer, and control operations. Key components include the Control Unit (CU), Arithmetic and Logic Unit (ALU), Accumulator, Program Counter (PC), Instruction Register (IR), Memory Module, and additional logic blocks.

Project_Report.pdf: Detailed project report.Verilog_Implementation/: Verilog HDL code for each module of the RISC processor.Accumulator.vALU.vBuffer.vControl_Unit.vInstruction_Register.vMemory_Module.vMUX.vProgram_Counter.vProcessor.v

Testing_and_Verification/: Test bench results for each module.

-

Clone the repository:

git clone https://github.com/Malisha4065/RISC-Processor.git -

Navigate to the

Verilog_Implementation/directory to access the Verilog code for each module. -

Open the Verilog files in a suitable development environment (e.g., Modelslim Vivado, Quartus Prime) for synthesis and simulation.

-

Explore the

Project_Report.pdffor a comprehensive overview of the project, including design rationale, methodology, and results.

- Dushmin Malisha

- Sahan Lelwala

- Sanjula Lakpahana