Jupiter is an open source and education-oriented RISC-V assembler and runtime simulator. It is written in Java and capable of simulate all the instructions of the base integer ISA (I extension) plus the M and F extensions (RV32IMF), including all the pseudo-instructions described in the user-level instruction set manual1. It was developed taking into account that it could be used in various courses such as: Computer Architecture, Compilers and Assembly Programming.

-

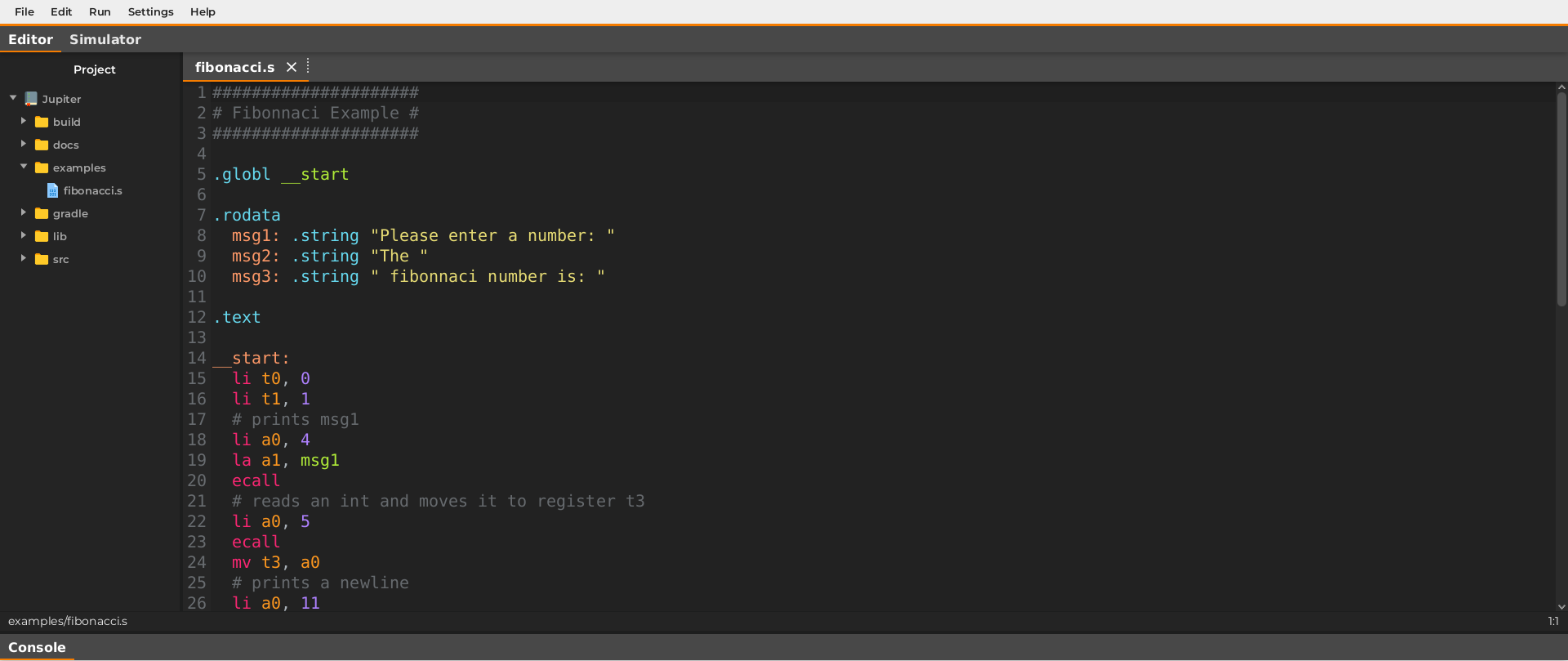

User Friendly: Jupiter was designed focused on education and for all the people that are getting to know the RISC-V architecture. It places for priority the user experience. Jupiter has two modes of operation (Command Line Interface and Graphical User Interface) and both of these were developed to be intuitive and easy to use.

-

Modularity: Jupiter can assemble and simulate several files at once, not everything has to be one file of 1,000 lines of code. Simply indicate by a global label what is the main starting point of the program. This permits modularity and enables the creation of projects and laboratories more easily.

-

Feedback: People using Jupiter gets feedback on what they are doing wrong 💯. The simulator shows different types of errors like: syntax errors, when trying to access reserved memory or when trying to write to a read-only memory.

-

Cross-platform: Jupiter is available for Linux (Ubuntu), macOS and Windows.

Please visit the following link for more info and documentation.

Download the app image for your operating system and unzip the file:

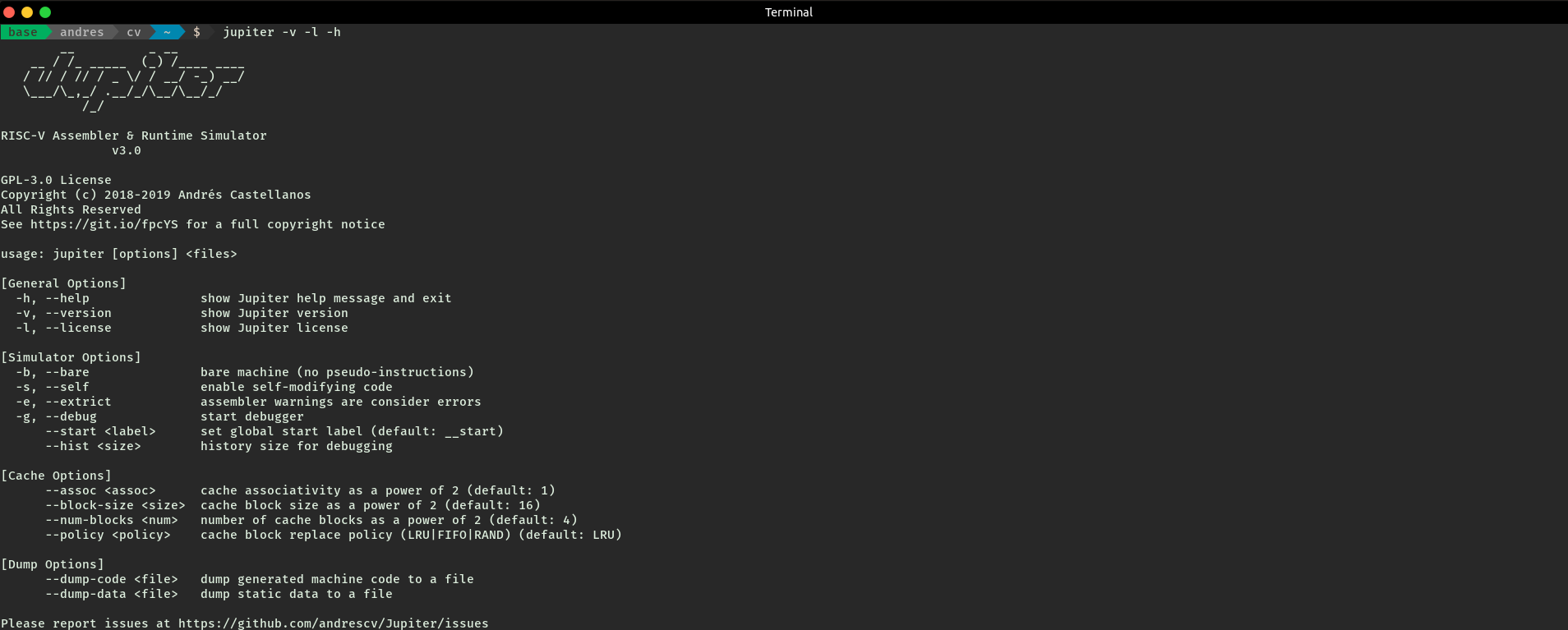

./image/bin/jupiter # for GUI mode

./image/bin/jupiter [options] <files> # for CLI modeimage\bin\jupiter # for GUI mode

image\bin\jupiter [options] <files> # for CLI modePull requests and stars are always welcome. For bugs and feature requests, please create an issue.

-

Venus: Berkeley's Web-based simulator originally developed by @kvakil and then updated and improved by @ThaumicMekanism.

-

RARS: RISC-V Assembler and Runtime Simulator (RARS), based on the originally MARS simulator, but refactored for the RISC-V architecture by @TheThirdOne.

-

Ripes: A graphical 5-stage RISC-V pipeline simulator & assembly editor developed by @mortbopet.

-

Spike: The original RISC-V ISA simulator that implements a functional model of one or more RISC-V harts.

A big thank you to all the people working on the RISC-V project.