In this project, a 32-bit multi-cycle MIPS processor that supports exceptions is implemented in Verilog HDL.

- This machine is designed to be able to execute a variety of instructions in a multicycle implementation.

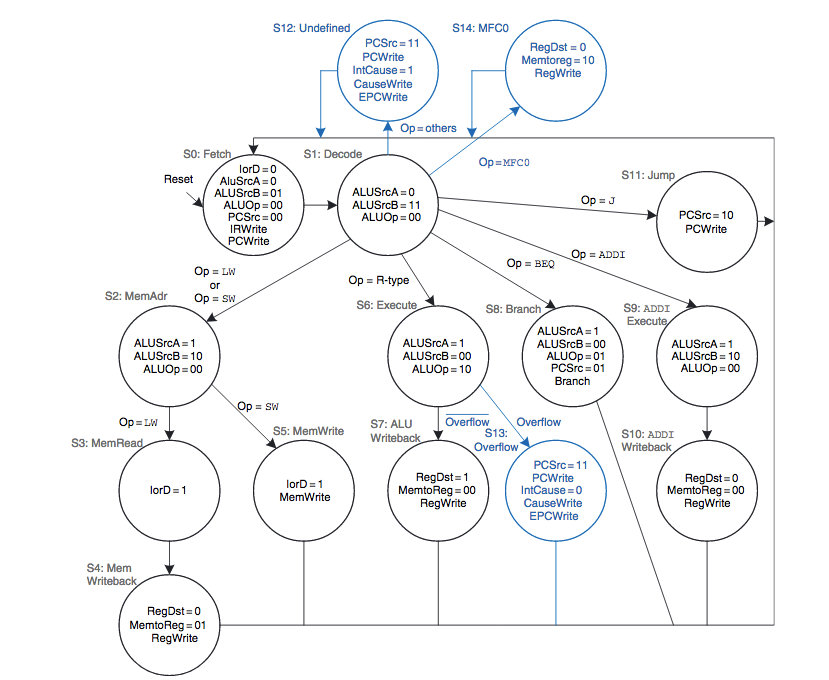

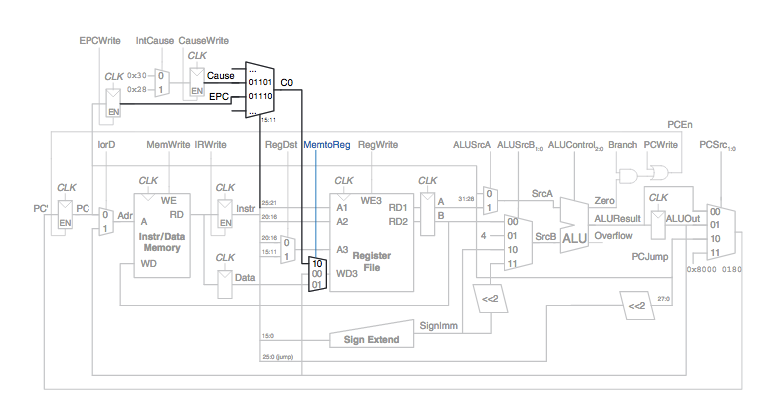

- The multicycle processor should support two types of exceptions: undefined instructions and arithmetic overflow.

The multicycle implementation breaks instructions down into multiple steps. These steps typically are the:

- Instruction fetch step

- Instruction decode and Register fetch step

- Execution, memory address computation, or branch completion step

- Memory access or R-type instruction completion step

- Memory read completion step

In each short step, the processor can read or write the memory or register file or use the ALU. Different instructions use different numbers of steps, so simpler instructions can complete faster than more complex ones. The processor needs only one adder; this adder is reused for different purposes on various steps. And the processor uses a combined memory for instructions and data. The instruction is fetched from memory on the first step, and data may be read or written on later steps. we add nonarchitectural state elements to hold intermediate results between the steps.

- Add : R[rd] = R[rs] + R[rt]

- Subtract : R[rd] = R[rs] - R[rt]

- And: R[rd] = R[rs] & R[rt]

- Or : R[rd] = R[rs] | R[rt]

- SLT: R[rd] = 1 if R[rs] < R[rt] else 0

- Lw: R[rt] = M[R[rs]+SignExtImm]

- Sw : M[R[rs]+SignExtImm] = R[rt]

- Beq : if(R[rs]==R[rt]) PC=PC+1+BranchAddr

- J : PC=JumpAddr

- Based on the provided instruction set, the data-path and control unit are designed and implemented.

This project needs Xlinx ISE and python3.

-

Download Full Installer for Linux from here. See How to install Xilinx ISE on Ubuntu.

-

Install Python 3.6 via command :

$ sudo apt-get install python3.6 -

Clone the repository.

-

Change the directory to MipsAssembler.

-

Type MIPS code to see it in binary form in src folder.

-

Synthesize and simulate the verilog design in src folder to see the results.

-

That's all !

- ⭕ Fix Control Branch