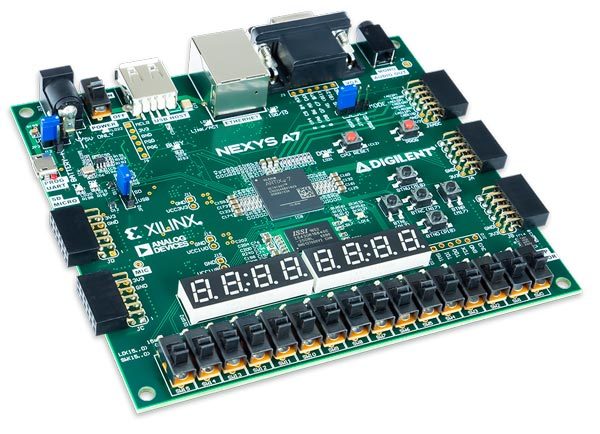

This is the project solution used in PLC2's 5-days class Professional VHDL. It develops step by step a stop watch running on a Digilent Nexys4 DDR board (new name Nexys A7).

Source: Digilent

- Digilent Nexys4 DDR / Nexys A7 board

- Micro-USB cable

- Vivado 2022.1 or later (released May. 2022)

| Button | Function |

|---|---|

Button reset (CPU RESET) |

reset |

Button up (BTNU) |

start / stop |

Button left (BTNL) |

unused |

Button center (BTNC) |

unused |

Button right (BTNR) |

unused |

Button down (BTND) |

unused |

| 7 (left most) | 6 | 5 | 4 | 3 | 2 | 1 | 0 (right most) |

|---|---|---|---|---|---|---|---|

| unused | unused | 10 min | 1 min | 10 sec | 1 sec | 1/10 sec | 1/100 sec |

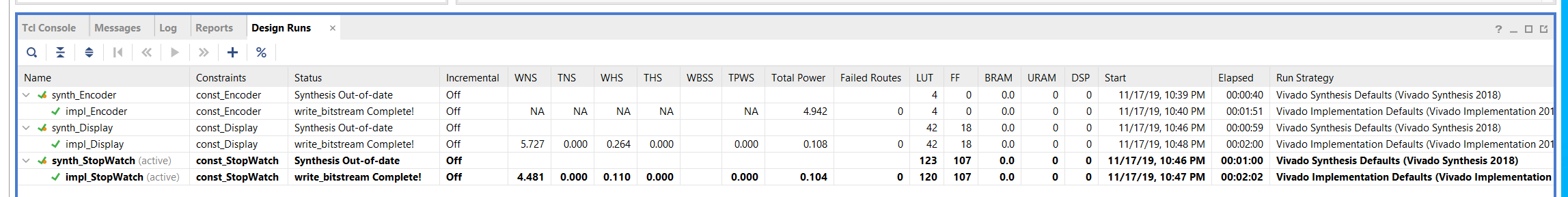

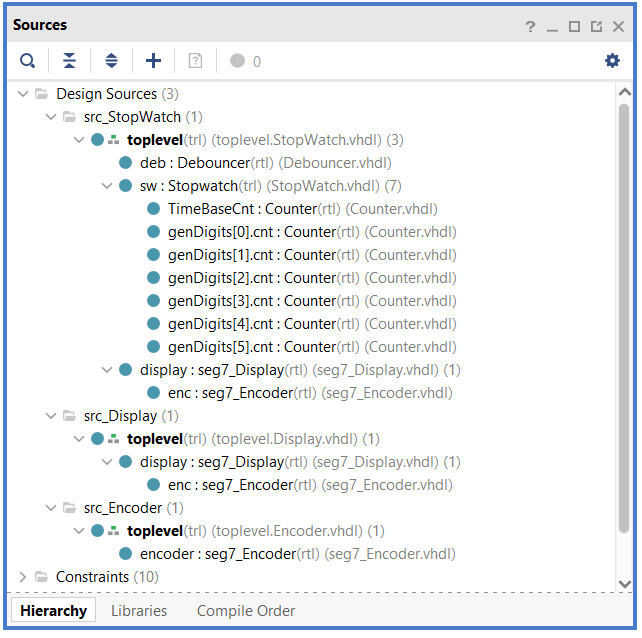

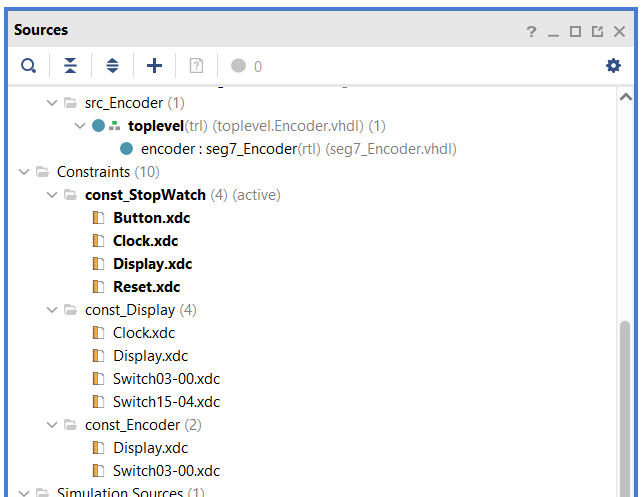

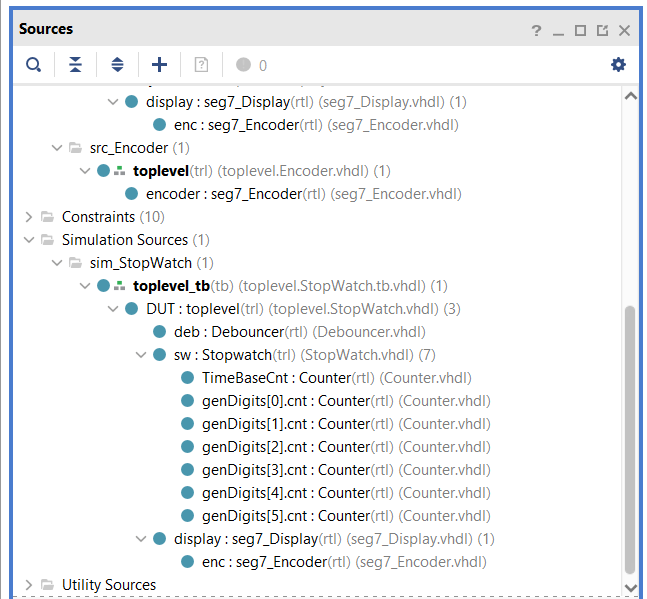

The repository provides 4 Vivado project files according to the progress of the class:

- 7-segment encoder

- 7-segment display

- Stop watch with simple timing settings

- Stop watch with MMCM and timing settings

| Design Hierarchy | Constraint Sets | Testbenches |

|---|---|---|

|

|

|

Licensed under MIT License.

SPDX-License-Identifier: MIT