The Arm architecture is a family of reduced instruction set computing (RISC) architectures for computer processors. In this project, a 32-bit pipelined ARM processor is implemented in Verilog HDL.

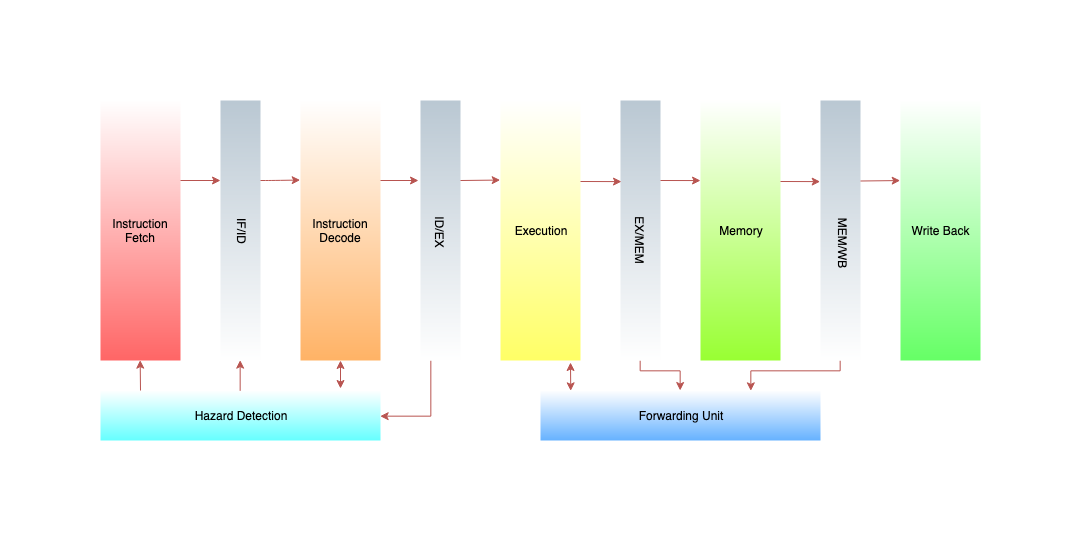

ARM pipeline has five stages, with one step per stage:

• IF: Instruction fetch from memory.

• ID: Instruction decode & register read.

• EX: Execute operation or calculate address.

• MEM: Access memory operand.

• WB: Write result back to register.

Each stage takes in data from that buffer, processes it and write into the next buffer. Also note that as an instruction moves down the pipeline from one buffer to the next, its relevant information also moves along with it.

| Instruction Mnemonic | Definition |

|---|---|

| MOV | Move |

| MVN | Move NOT |

| ADD | Add |

| ADC | Add with Carry |

| SUB | Subtract |

| SBC | Subtract with Carry |

| AND | Logical AND |

| ORR | Logical OR |

| EOR | Exclusive OR |

| CMP | Compare |

| TST | Test |

| LDR | Load Register |

| STR | Store Register |

| B | Branch |

This project needs Icarus-Verilog and a VCD viewer.

-

Icarus-Verilog can be installed via Homebrew :

$ brew install icarus-verilog -

Download Scansion from here.

-

Clone the repository.

-

Run

$ makeand type MIPS code to see it in binary form in rams_init_file.hex file. -

$ make simulatewill:

- compile design+TB

- simulate the verilog design

$ make displaywill:

- display waveforms.

- ⭕ Add more instructions