This repository contains a raw UART module implemented in Verilog. Currently only sending from the FPGA is supported. The implementation of the rx direction will follow soon

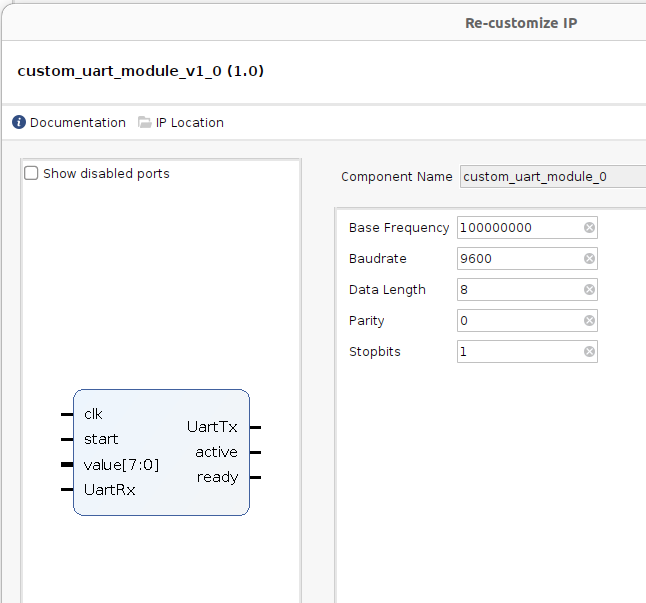

It provides the following input and output connections:

| Signal | Description |

|---|---|

| clk | Input clock must match the parameter Base Frequency |

| start_signal | Must be set to HIGH until the active signal changes to HIGH. |

| value | 8 Bit input value to write. |

| UartRx | Input rx signal reading data from the UART bus. |

| UartRx | Output tx signal to send data on a UART but |

| active | HIGH indicates that the module is currently processing. |

| ready | Indicating for one clock cycle that the current task was executed |

| Parameter | Description |

|---|---|

| Base Frequeny | Input frequency in Hz. |

| Baudrate | Number of chars per time unit. Possible deviations occur when the base frequency is not devidable by the base frequency! |

| Data Length | Currently only 8 bit supported. |

| Parity | Supported 0: None, 1: Even, 2: Oddd |

| Stopbits | 1 or 2 stopbits are supported |

The module can be added to the block diagram, by adding the ip folder to the IP-catalog as repository.

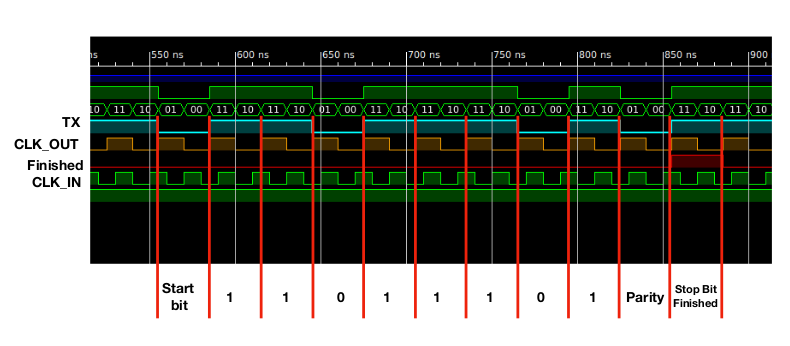

The module was tested and verified by a test bench.

This figure shows a simulation of the verilog module sending 11011101 (187) with parity even and one stop bit.

It was developed and tested on a Digilent Atlys board using a Xilinx Spartan-6 FPGA as well as a PYNQ Z2.