DRIM4HLS is the first model of a 32b RISC-V processor designed with SystemC and Matchlib's Connections. The SystemC model is synthesized with High-level synthesis achieving an full-throughput pipeline dataflow. The baseline functionality of the processor is based on the HL5 core from Columbia University. DRIM4HLS was synthesized using Mentor's Catapult 2021.1.1 and verified with QuestaSim 2019.3_1. The RTL produced was also validated in an FPGA prototype using Xilinx Nexy 7 board.

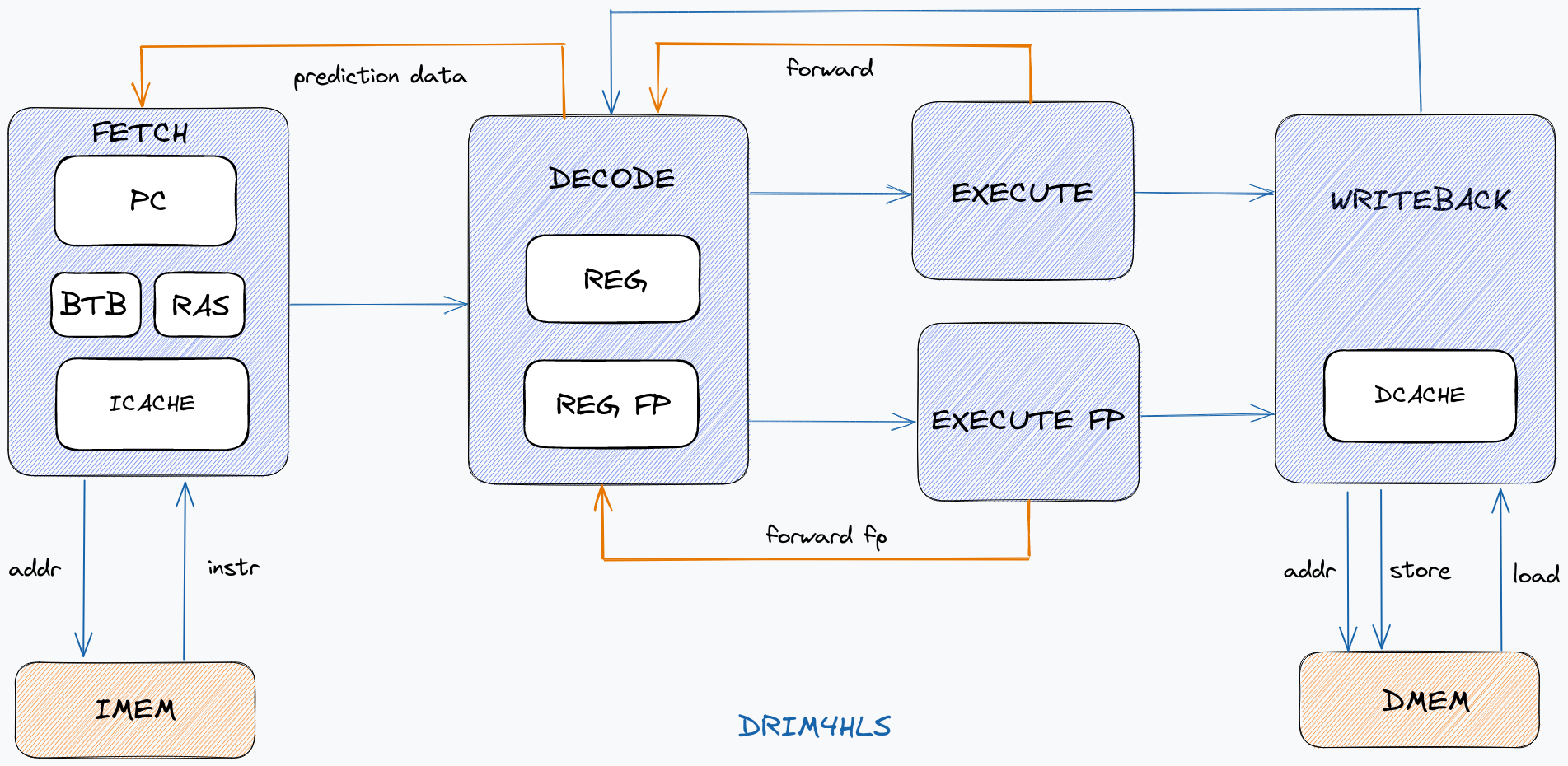

The organization of the SystemC model of DRIM4HLS is shown in the following figure

The blue blocks are part of the processor while the instruction and data memories are used only for simulation. No specific latency is assumed by the memories. All blocks of the processor communicate using the Connections flow-controlled channels (ready/valid). In this way the stalling of instruction execution that naturally appears in all pipelined processors can be smoothly handled by the flow control mechanism inherent in the operation of Connections.

DRIM4HLS can be simulated using open-source libraries without requiring any other tools.

In the future the baseline pipelined processor will be enhanced with multiple architectural features such as branch prediction and caches that will improve its performance.

The repository contains various versions of the processor. Check the respective folder for a schema of the particular version.

core/ - contains the core version of the processor.

caches/ - in addition to the core functionality of the processor, N-associative instruction/data caches are implemented.

prediction/ - in addition to the cached version of the processor, branch prediction and a return address stack for jump instructions is provided.

floating_point/ - in addition to the version of the processor with branch/jump prediction, support for floating point instructions is provided.

In order to simulate DRIM4HLS you would need gcc (testted on version 9.4) and SystemC (tested on version 2.3.3). You can download SystemC from here. Also you would need the header-only libraries of Connections, AC_SIMUTILS and AC_TYPES.

To synthesize the design to RTL you would need a license for Catapult HLS. Also for simulating RTL any logic-level simulator will suffice. We synthesized the processor with Catapult HLS 2021.1.1 and simulatd the RTL with QuestaSim 2019.3_1.

The model of DRIM4HLS already incorporates all the pieces needed to run the post-synthesis SCVerify flow of Catapult for automatic RTL verification.

A Makefile is provided inside the project directory in order to easily compile DRIM4HLS. The Makefile uses the following variables:

HOMESYSTEMC_HOMEAC_SIMUTILS_HOMEAC_TYPES_HOME

Build the SystemC simulation executable by typing:

make build

Run the SC simulation by typing:

./sim_sc

In each version of the processor a .tcl script is provided containing all the necessary instructions for compiling, scheduling and synthesizing the DRIM4HLS processor using Catapult.

To use the .tcl script just run:

catapult -f <processor_version>/go_hls_ic.tcl

The repository contains a folder called examples, containing multiple small-scale programs for simulating the processor. In order to execute a testing program, a .txt file containing the instructions of the program must be passed to the executable sim_sc.

cd examples/<program_name>

./sim_sc <program_name.txt>

The simulation of the core will produce two .txt files in the project directory. The initial_dmem.txt representing the memory of the core after loading the program and the report_dmem.txt representing the memory of the core after the execution of the testing program.

In order to generate your own testing programs from some C code, the RISC-V GNU Compiler Toolchain is needed. The provided testing programs in the examples folder used the 8.2.0 version of the toolchain.

Clone the repository from the above link and follow the instructions for downloading several standard packages needed to to build the toolchain.

The following commands will configure the toolchain and build it.

./configure --prefix=<custom_path> --enable-multilib

make

Change <custom_path> to the desired location, for example /opt/riscv.

Furthermore, a linker script, lscript, is needed (provided inside the examples folder) and a file, bootloader, with assembly code which calls the main() function (provided inside the examples folder).

Before compiling the C code riscv64-unknown-elf-gcc must be in $PATH. In order to add it, run:

export PATH=/<custom_path>/bin:$PATH

To compile some C code and create an object ELF file, run:

riscv64-unknown-elf-gcc -O3 -march=rv32ima -mabi=ilp32 -T lscript bootstrap.s notmain.c -o notmain.elf -nostdlib

SREC files conveys binary information as hex values. In order to create the file run:

riscv64-unknown-elf-objcopy -O srec --gap-fill 0 notmain.elf notmain.srec

A .txt file containing the initial state of the core's memory (instructions and data) after the testing program is loaded is needed. This file will be passed as an argument to the core in order to start the simulation. To create the .txt from the .srec file, the srec2text.py script from HL5 is used (also contained inside examples folder).

./srec2text.py notmain.srec > notmain.txt

Finally, the notmain.txt is reade and can be used to simulate the testing program on the core.