SCARV: processor core implementation

Acting as a component part of the wider SCARV project, the RISC-V compatible SCARV micro-controller (comprising a processor core and SoC) is the eponymous, capstone output, e.g., representing a demonstrator for the research oriented XCrypto ISE and the industry oriented RISC-V Scalar Cryptography ISE. The main repository acts as a general container for associated resources; this specific submodule houses the processor core implementation.

Branches:

master- Main branch for XCrypto related work.riscv/crypto-ise- Main branch for RISC-V Crypto ISE implementation.scarv/skywater/main- Main branch for Skywater tapeout project.dev/paper/aes-n-ways- Development branch for RISC-V AES ISE Evaluation.scarv/xcrypto/masking-ise- Development branch for Software masking ISE.

Contents:

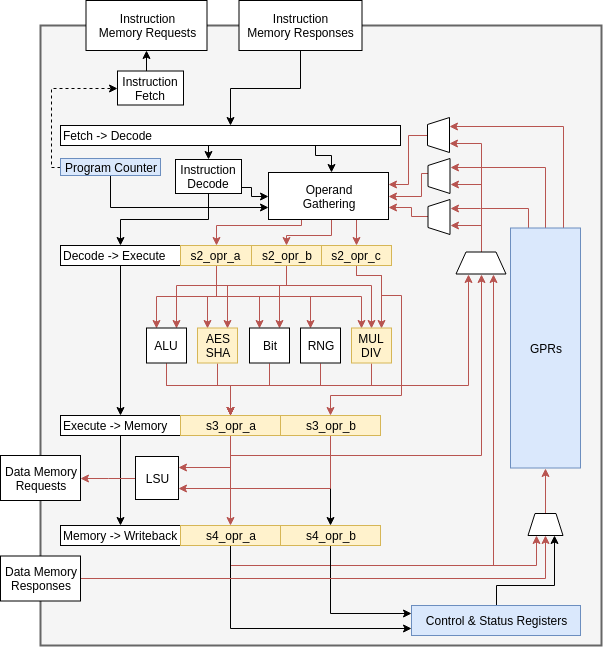

This is a 5-stage single issue in order CPU core, implementing the RISC-V 32-bit integer base architecture, along with the Compressed and Multiply extensions. It's a micro-controller, with no cache, branch prediction or virtual memory.

See the docs/ folder for information on the design requirements and

the pipeline structure.

- Design Requirements

- Functional Verification

- Implementation Documentation:

-

Install the following tools installed to use all parts of the design flow:

-

A Toolchain which supports the XCrypto instruction set extension.

-

Checkout the repository and required submodules.

$> git clone git@github.com:scarv-cpu/scarv-cpu.git $> cd scarv-cpu/ $> git submodule update --init --remote

-

Setup tool environment variables.

$> export YOSYS_ROOT=<path to yosys installation> $> export RISCV=<path to toolchain installation>

-

Configure the project environment.

$> source bin/conf.sh

-

Build the verilator simulation model:

$> make verilator_build -

Run the basic RISC-V compliance tests:

$> make riscv-compliance-build $> make riscv-compliance-run

-

Run the standard Yosys Synthesis flow:

$> make synthesise

This work has been supported in part by EPSRC via grant EP/R012288/1, under the RISE programme.