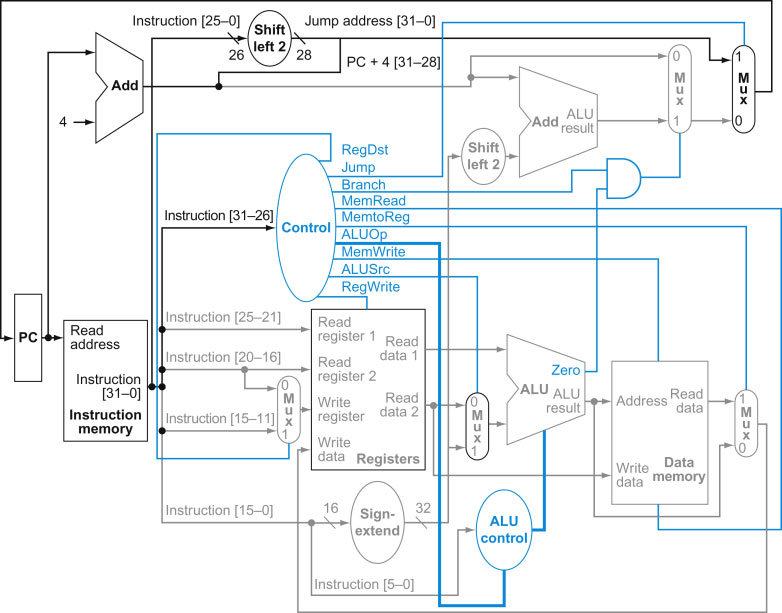

Trying to implement a single cycle MIPS computer in Verilog that supports MIPS assembly instructions including:

- Memory-reference instructions load word

lwand store wordsw - Arithmetic-logical instructions

add,addi,sub,and,andi,or, andslt - Jumping instructions branch-equal

beqand jumpj

Below image is the Risc processor I am trying to impleent, But end product may not be exactly the same.

img_src: Click Here