Update

Finally implemented the interrupt function after load and matmul is finished. I also made the main.c file a little bit cleaner

by using header files for interrupt and XGPIO initialization and the matrix references.

Next version would be adding new memory spaces for additional matrices in the PL fabric which would allow us to write

multiple matrices then switch to whatever matrix we want for matrix multiplication by specifying which matrices to load

to the registers.

I am also planning to add some features to specify if the matrix to be written on to the FPGA is a weight or input matrix

so we can "automatically" transpose the matrix. As of now, the matrix we have is transposed by default.

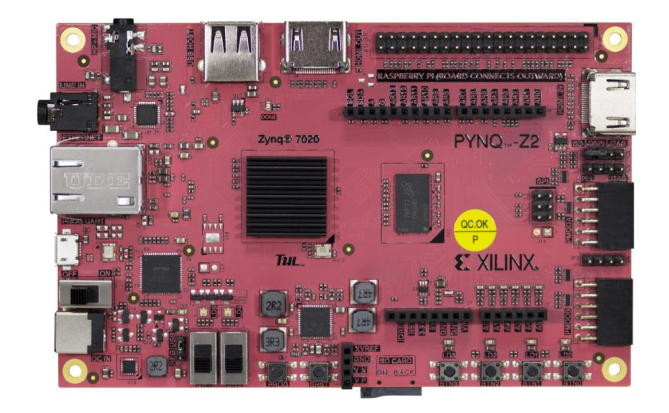

- PS Clock Frequency: 650 MHz

- PL Clock Frequency: 100 MHz

- Matrix Multiplication: 1 us latency (8x8 matmul)

- Total (Write, Load, Matmul, Read): 0.042003 s

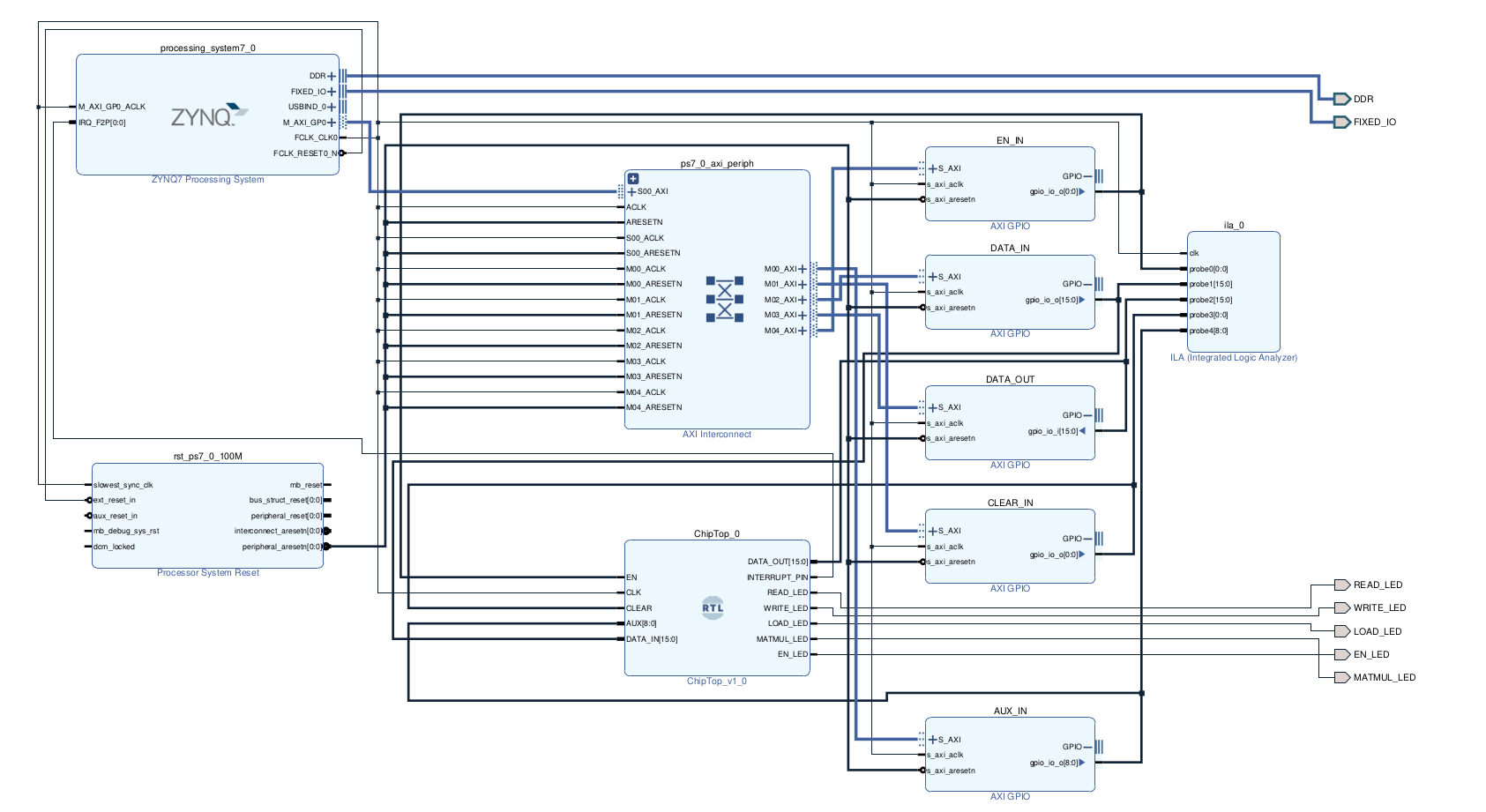

Block Diagram

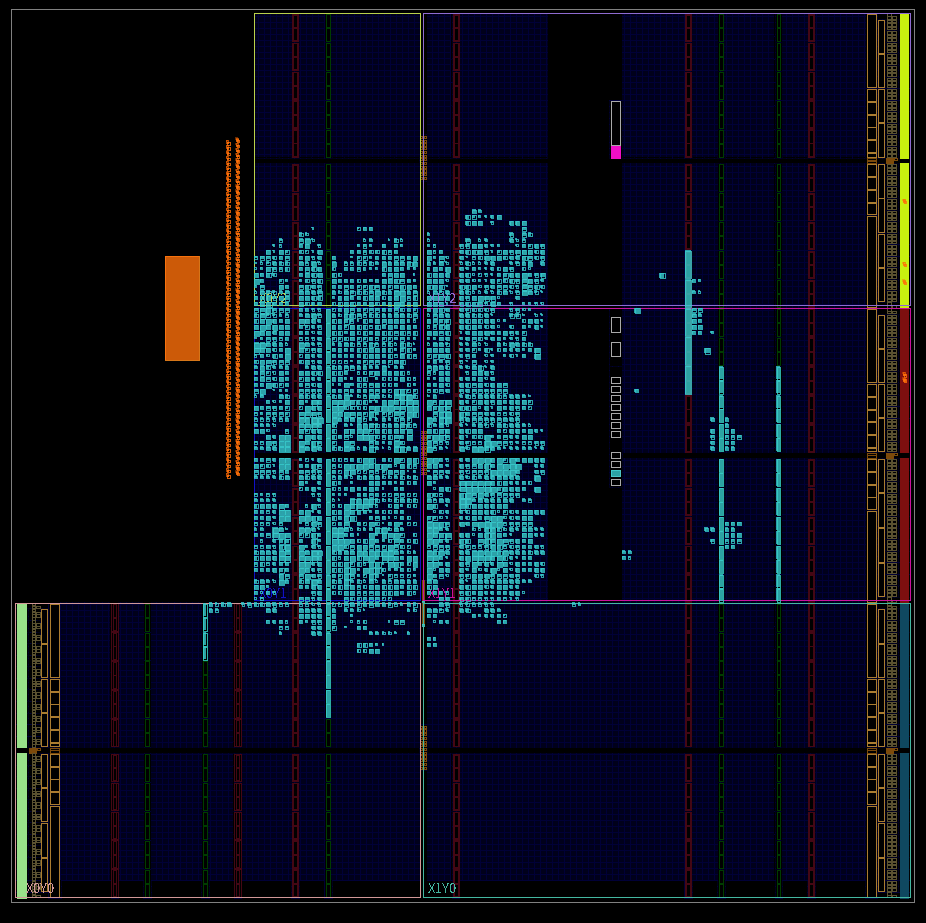

Floor Planning

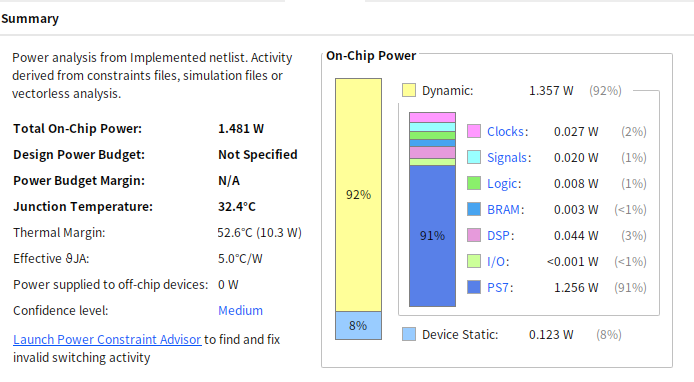

Power Summary

Timing Summary

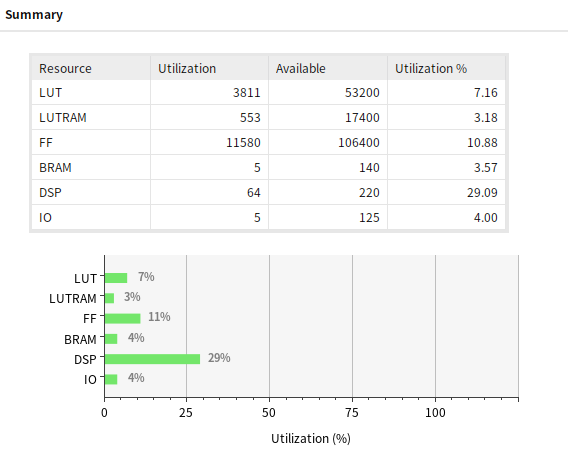

Utilization Summary